54

DS726PP2

CS4525

6.2

Hardware Mode

A limited feature set is available when the CS4525 powers up in hardware mode. The available features are

described in the following sections. All device configuration is achieved via hardware control input pins.

6.2.1

System Clocking

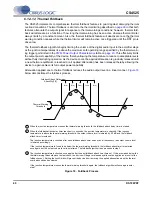

In hardware mode, the CS4525 must be clocked by a stable external clock source input on the SYS_CLK

pin. This input clock is used to synchronize the input serial audio signals with the internal clock domain

and to clock the internal digital processing, sample-rate converter, and PWM modulators. It is also used

to determine the sample rate of the serial audio input signals in order to automatically configure the vari-

ous internal filter coefficients.

To ensure proper operation, the CS4525 must be informed of the nominal frequency of the supplied

SYS_CLK signal via the ClkFreq[1:0] hardware control pins. These pins must be set to the appropriate

level before the RST signal is released to initiate a power-up sequence. The nominal clock frequencies

indicated by the states of the ClkFreq[1:0] pins are shown in

below. See the

table on

for complete input frequency range specifications.

WARNING: The SYS_CLK signal must never be removed or stopped while the RST pin is high and any

of the power output stages are connected to a load. Doing so may result in permanent damage to the

CS4525 and connected transducers.

below demonstrates a typical clocking configuration using the SYS_CLK input.

6.2.2

Power-Up and Power-Down

The CS4525 will remain in a completely powered-down state until the RST pin is brought high.

6.2.2.1

Recommended Power-Up Sequence

1.

Hold RST low until the power supplies and the input SYS_CLK signal are stable.

2.

Bring RST high.

Hardware mode will be entered after approximately 10 ms.

ClkFreq1

ClkFreq0

Nominal SYS_CLK Frequency

Low

Low

18.432 MHz

Low

High

24.576 MHz

High

Low

27.000 MHz

High

High

Reserved

Table 13. SYS_CLOCK Frequency Selection

SYS_CLK

RST

DSP

Reset_Out

Clock_In

Clock

XTI

XTO

Figure 22. Typical SYS_CLK Input Clocking Configuration

CS4525