ADM1026

PRELIMINARY TECHNICAL DATA

– 2 0 –

REV. PrL

PRELIMINAR

Y

TECHNICAL

DA

TA

FAN INPUTS

Pins 3 to 6 and 9 to 12 may be configured as fan speed

measuring inputs by clearing the corresponding bit(s) of

Configuration Register 2 (address 01h) or as general-pur-

pose logic inputs/outputs by setting bits in this register.

The power-on default value for this register is 00h, which

means all the inputs are set for fan speed measurement.

Signal conditioning in the ADM1026 accommodates the

slow rise and fall times typical of fan tachometer outputs.

The maximum input signal range is 0 to +6.5V, even

where V

CC

is less than 5V. In the event that these inputs

are supplied from fan outputs which exceed 0 to 6.5V, ei-

ther resistive attenuation of the fan signal or diode clamp-

ing must be included to keep inputs within an acceptable

range.

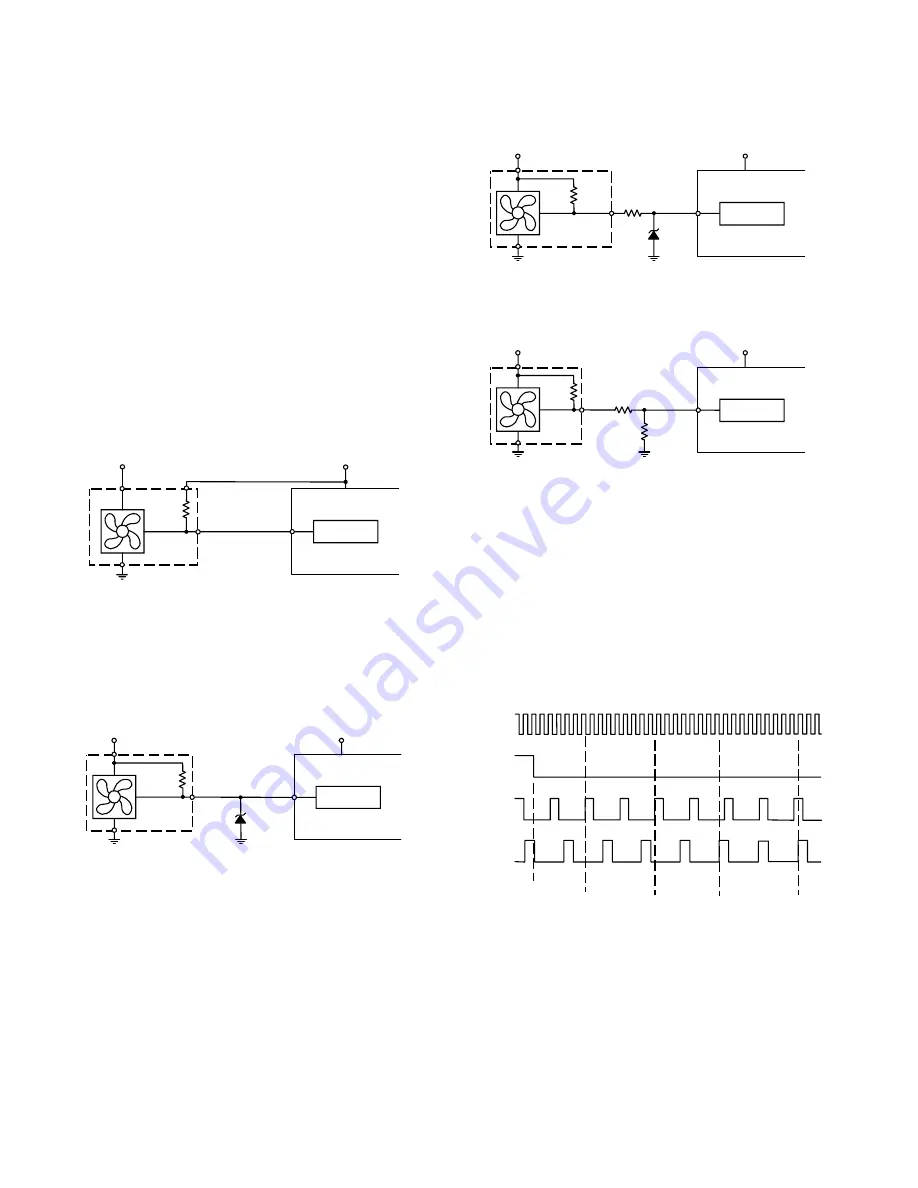

Figures 12a to 12d show circuits for most common fan

tacho outputs.

If the fan tacho output has a resistive pullup to V

CC

then it can

be connected directly to the fan input, as shown in figure 12a.

+1 2 V

F A N S P E E D

C O U N T E R

F AN (0-7)

P ULL UP

4.7k

⍀

⍀

⍀

⍀

T YP .

T A C H O

O U T P U T

V

C C

Figure 12a. Fan With Tach Pullup To +V

CC

.

If the fan output has a resistive pullup to +12V (or other

voltage greater than 6.5V) then the fan output can be

clamped with a zener diode, as shown in figure 12b. The

zener voltage should be chosen so that it is greater than

V

IH

but less than 6.5V, allowing for the voltage tolerance

of the zener. A value of between 3V and 5V is suitable.

+1 2 V

F A N S P E E D

C O U N T E R

F AN (0-7)

T A C H O

O U T P U T

Z D 1 *

Z E N E R

P ULL UP

4.7k

⍀

⍀

⍀

⍀

T YP .

*C HO O S E Z D1 V O L T AG E AP P RO X . 0 .8 x V

C C

V

C C

Figure 12b. Fan with Tach. Pullup to Voltage >6.5V e.g.

12V) Clamped with Zener Diode

If the fan has a strong pullup (less than 1k

⍀

) to +12V, or

a totem-pole output, then a series resistor can be added to

limit the zener current, as shown in figure 11c. Alterna-

tively, a resistive attenuator may be used, as shown in fig-

ure 12d.

R1 and R2 should be chosen such that:

2V < V

PULLUP

x R2/(R

PULLUP

+ R1 + R2) < 5V

The fan inputs have an input resistance of nominally

160k

⍀

to ground, so this should be taken into account

when calculating resistor values.

With a pullup voltage of 12V and pullup resistor less than

1k

⍀

, suitable values for R1 and R2 would be 100k

⍀

and

47k

⍀

.This will give a high input voltage of 3.83V.

+1 2 V

F A N S P E E D

C O U N T E R

F AN (0-7)

P UL L UP

T Y P . <1k

⍀

⍀

⍀

⍀

O R T O T E M -P O L E

Z D 1

Z E N E R*

R1

10k

⍀

⍀

⍀

⍀

T A C H O

O /P

*C HO O S E Z D1 V O L T AG E AP P RO X . 0 .8 x V

C C

V

C C

Figure 12c. Fan with Strong Tach. Pullup to >V

CC

or Totem-

Pole Output, Clamped with Zener and Resistor

+1 2 V

F A N S P E E D

C O U N T E R

F AN (0-7)

T A C H O

O U T P U T

R 1 *

R 2 *

<1k

⍀

⍀

⍀

⍀

V

C C

*S E E T E X T

Figure 12d. Fan with Strong Tach. Pullup to >V

CC

or Totem-

Pole Output, Attenuated with R1/R2

FAN SPEED MEASUREMENT

The fan counter does not count the fan tacho output pulses

directly, because the fan speed may be less than 1000 RPM

and it would take several seconds to accumulate a reason-

ably large and accurate count. Instead, the period of the fan

revolution is measured by gating an on-chip 22.5kHz oscil-

lator into the input of an 8-bit counter for two periods of

the fan tacho output, as shown in Figure 13, so the accumu-

lated count is actually proportional to the fan tacho period

and inversely proportional to the fan speed.

22.5kHz

CLOCK

CONFIG

RE G. 1 BIT 0

FAN0

INP UT

FAN0

M E AS URE M E NT

P E RIO D

FAN1

M E AS URE M E NT

P E RIO D

S TART O F

M ONITORING

CY CLE

FAN1

INP UT

1

2

3

4

1

2

3

4

Figure 13. Fan Speed Measurement

The monitoring cycle begins when a one is written to the

Monitor Bit (bit 0 of Configuration Register 1). The

INT

_Enable (Bit 1) should be set to one to enable the

INT

output.

Speed measurement of the Fan 0 channel is initialized on

the first rising edge of the fan tach pulse after Start goes

low, and oscillator pulses are actually counted from the

second rising tach edge to the fourth rising edge. The

measurement then switches to Fan 1. Here again, the

measurement is initialized on the first tach pulse rising

edge after the Fan 0 measurement finishes and oscillator