92 SBC347A 3U VPX Single Board Computer

Publication No. 500-9300527837-000 Rev. A.0

7.1.11 Signal Descriptions

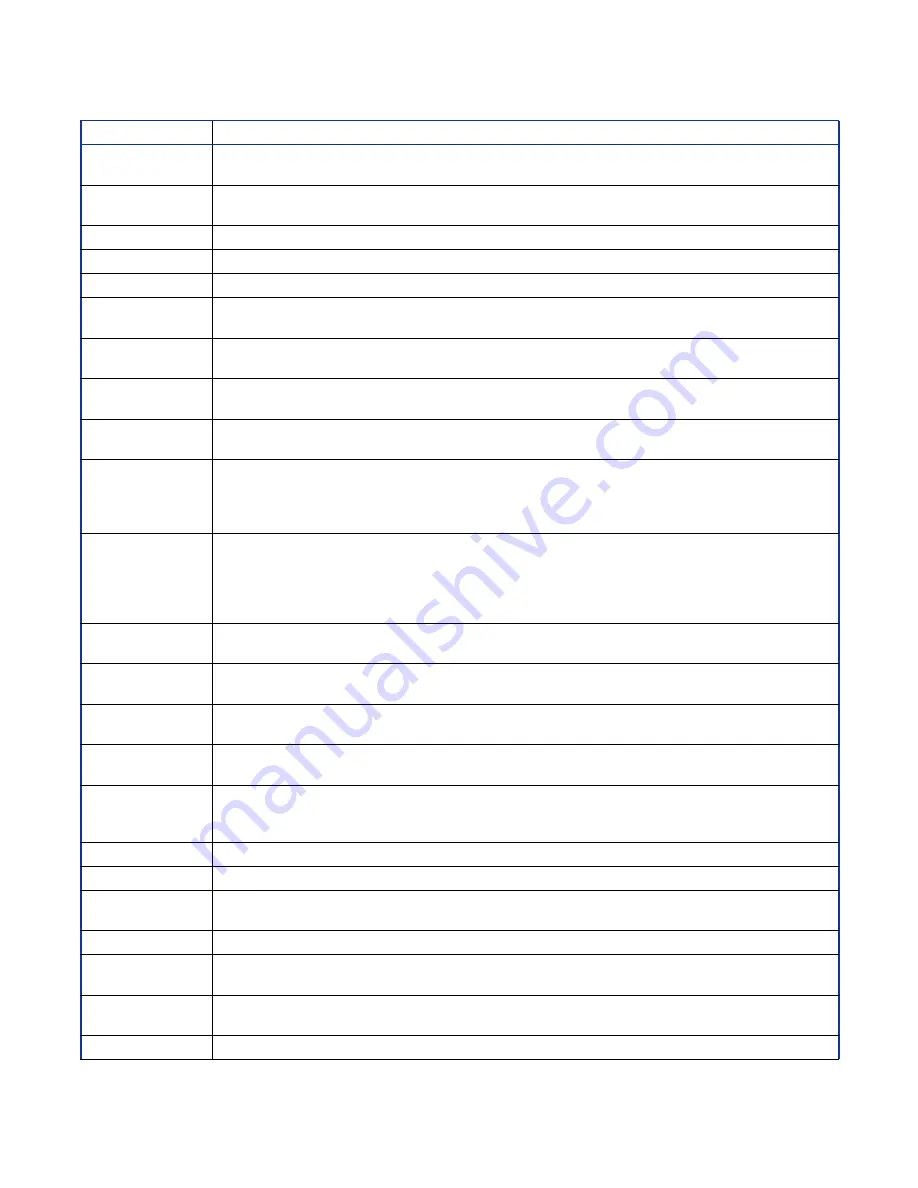

Table 7-12 Backplane Connector Signal Descriptions

Name

Description

VS2, VS3

VPX Vs2 (+3.3 V) and Vs3 (+5 V) power inputs. See

Section A.2 "Electrical Specification"

more details.

P3V3_AUX

VPX +3.3 V DC auxiliary power input. See

Section A.2 "Electrical Specification"

for more

details.

GND

The DC voltage reference for the system

None

No signals specified in VPX specification

N/C

No Connection

GA[4:0]~

Geographical Addressing bits. These are used to set the slave address of the SBC347A. The settings

are reflected in the FPGA

Backplane Status Register (0x6CA)

.

GAP~

Geographical addressing parity bit input. The sum of all GA bits, including the parity bit, should be an

odd number. The setting is reflected in the FPGA

Backplane Status Register (0x6CA)

.

SM0_CLK,

SM1_DATA

System Management bus A clock and data. Connected to the BMM via I

2

C buffers. These allow access

to certain onboard resources from an external I

2

C master.

SYSRESET~

System Reset. When this is low, it causes the system to be reset. The SBC347A generates SYSREST~

when it is configured as System Controller.

NVMRO

Nonvolatile Memory Read Only. When this signal is high, all onboard nonvolatile memory is write-

protected. This signal can be externally pulled low (using a link on the backplane or RTM) or driven low

under software control by the SBC347A if configured as System Controller. The FPGA

shows the state.

JTAG_TCLK,

JTAG_TDO,

JTAG_TDI,

JTAG_TMS,

JTAG_TRST~

JTAG Test Clock,

Test Data Out (Tx from SBC347A),

Test Data In (Rx to SBC347A from test device),

Test Mode Select and

Test Reset

REF_CLK_P/N

OpenVPX Reference Clock differential signals. Optionally used as 100 MHz PCIe REFCLK transmit/

receive on the SBC347A.

PCIE_DP01_TXyP/N,

PCIE_DP01_RXyP/N

PCIe Data Plane x4 link transmit and receive differential pair y (y = 0 to 3)

PCIE_DP00_TXyP/N,

PCIE_DP00_RXyP/N

PCIe Control Plane x2 link transmit and receive differential pair y (y = 0 to 1)

PCIE_CPU_RXyP/N,

PCIE_CPU_TXyP/N

PCIe Data Plane y (y = 0 to 7) transmit and receive differential pairs

SATAn_TXP/N,

SATAn_RXP/N

SATA interface n (n = 0 to 2) transmit and receive differential pairs. TX is from the SBC347A to an

external SATA device; RX is from an external SATA device to the SBC347A. Both ports are Rev 3

capable.

USBx_DATA_P/N

USB2.0 port n (n = 0 to 3) differential pair

USB0_1_PWR

USB ports 0 and 1 power (shared, maximum 1A for both ports)

USB2_PWR,

USB3_PWR

USB ports 2 and 3 power

GPIO[7:0]

GPIO. GPIO2 is shared with AXIS_CLK and GPIO3 is shared with AXIS_RST

AXIS_CLK,

AXIS RST

AXIS clock and reset signals respectively (required for Abaco AXIS software support). If AXIS support is

required, the signals cannot be used as GPIO.

ETHn_xP/N,

ETHn_xP/N

10 GbE channel n (n = 1 or 2) receive and transmit signal x (x = 0 to 3) differential pair.

10GBASE-T operation.

VBAT

3 V battery supply input to back up RTC