ZC706 Evaluation Board User Guide

41

UG954 (v1.5) September 10, 2015

Feature Descriptions

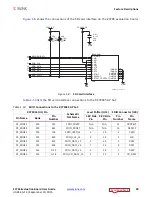

lists the GTX Banks 109 and 110 interface connections between the AP SoC U1

and FMC HPC connector J37.

Table 1-14:

AP SoC GTX Banks 109 and 110 Interface Connections to FMC HPC J37

Transceiver

Bank

AP SoC U1

Pin

Number

AP SoC U1 Pin Name

Schematic Net Name

Connected

Pin

Connected

Device

GTX_BANK_109

AK10

MGTPTXP0_109

FMC_HPC_DP0_C2M_P

C2

FMC HPC

J37

AK9

MGTPTXN0_109

FMC_HPC_DP0_C2M_N

C3

AH10

MGTPRXP0_109

FMC_HPC_DP0_M2C_P

C6

AH9

MGTPRXN0_109

FMC_HPC_DP0_M2C_N

C7

AK6

MGTPTXP1_109

FMC_HPC_DP1_C2M_P

A22

AK5

MGTPTXN1_109

FMC_HPC_DP1_C2M_N

A23

AJ8

MGTPRXP1_109

FMC_HPC_DP1_M2C_P

A2

AJ7

MGTPRXN1_109

FMC_HPC_DP1_M2C_N

A3

AJ4

MGTPTXP2_109

FMC_HPC_DP2_C2M_P

A26

AJ3

MGTPTXN2_109

FMC_HPC_DP2_C2M_N

A27

AG8

MGTPRXP2_109

FMC_HPC_DP2_M2C_P

A6

AG7

MGTPRXN2_109

FMC_HPC_DP2_M2C_N

A7

AK2

MGTPTXP3_109

FMC_HPC_DP3_C2M_P

A30

AK1

MGTPTXN3_109

FMC_HPC_DP3_C2M_N

A31

AE8

MGTPRXP3_109

FMC_HPC_DP3_M2C_P

A10

AE7

MGTPRXN3_109

FMC_HPC_DP3_M2C_N

A11

AD10

MGTREFCLK0P_109

FMC_HPC_GBTCLK0_M2C_C_P

D4

AD9

MGTREFCLK0N_109

FMC_HPC_GBTCLK0_M2C_C_N

D5

AF10

MGTREFCLK1P_109

NC

NA

NA

AF9

MGTREFCLK1N_109

NC

NA

NA