www.ti.com

31

0

1

2

15

23

7

27

11

19

3

29

o

w

n

e

r

s

h

i

p

t

e

a

r

d

o

w

n

e

o

p

e

o

q

s

o

p

3

reserved

cc

message_length

13

21

5

25

9

17

1

30

14

22

6

26

10

18

2

28

12

20

4

24

8

16

0

Bit Fields

next_descriptor_pointer

buffer_pointer

src_id

pri

tt

reserved

mailbox

Word

Offset

SRIO Functional Description

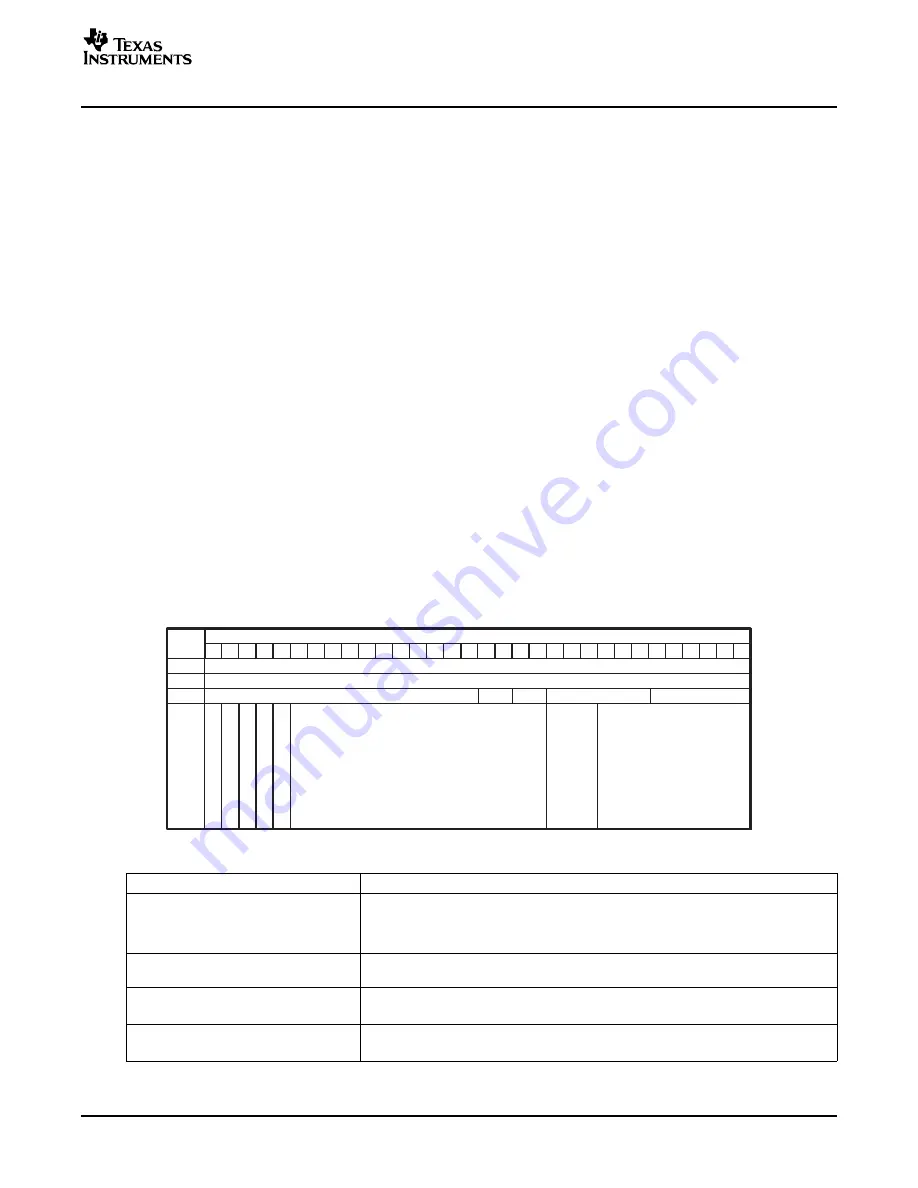

If a RX message’s length is greater than that of the targeted buffer descriptor, an ERROR response is

sent back to the source device. In addition, the DSP is notified with the use of the CC field of the RX CPPI

buffer descriptor, described as follows. This situation can result from a DSP software error (misallocating a

buffer for the queue), or as a result of sender error (sending to a wrong mailbox).

An RX transaction timeout is used by all multi-segment queues, in order to not hang receive mailbox

resources in the event that a message segment is lost in the fabric. This response-to-request timer

controls the time-out period for sending a response packet and receiving the next request packet of a

given multi-segment message. It has the same value and is analogous to the request-to-response timer

discussed in the TX CPPI and LSU sections, which is defined by the 24-bit value in the port response

time-out CSR (See

Section 2.3.3.3

). The RapidIO Interconnect Specification states that the maximum time

interval (all 1s) is between 3 and 6 seconds. Each multi-segment receive timer requires a 4-bit register.

The register is loaded with the current timecode when the response is sent. Each time the timecode

changes, a 4-bit compare is done to the register. If the register becomes equal to the timecode again,

without the next message segment being seen, then the transaction has timed out. If this happens, the RX

buffer resources can be released.

The buffer descriptor points to the corresponding data buffer in memory and also points to the next buffer

descriptor in the queue. As segments of a received message arrive, the msgseg field of each segment is

monitored to detect the completion of the received message. Once a full message is received, the

OWNERSHIP bit is cleared in the packet’s buffer descriptor to give control to the host. At this point, a host

interrupt is issued. This interface works with programmable interrupt rate control. There is an ICSR bit for

each supported queue. On interrupt, the CPU processes the RX buffer queue, detecting received packets

by the status of the OWNERSHIP bit in each buffer descriptor. The host processes the RX queue until it

reaches a buffer descriptor with a set OWNERSHIP bit, or set EOQ bit. Once processing is complete, the

host updates the RX DMA State Completion Pointer, allowing the peripheral to reuse the buffer.

Figure 19

shows the RX buffer descriptor fields and

Table 18

describes them. A RX buffer descriptor is a

contiguous block of four 32-bit data words aligned on a 32-bit boundary. Accesses to these registers are

restricted to 32-bit boundaries.

Figure 19. RX Buffer Descriptor Fields

Table 18. RX Buffer Descriptor Field Descriptions

Field

Description

next_descriptor_pointer

Next Descriptor Pointer: The 32-bit word aligned memory address of the next buffer

descriptor in the RX queue. This references the next buffer descriptor from the current

buffer descriptor. If the value of this pointer is zero, then the current buffer is the last

buffer in the queue. The DSP core sets the next_descriptor_pointer.

buffer_pointer

Buffer Pointer: The byte aligned memory address of the buffer associated with the

buffer descriptor. The DSP core sets the buffer_pointer.

sop = 1

Start of Message: Indicates that the descriptor buffer is the first buffer in the message.

•

This bit will always be set, as this device only supports one buffer per message.

eop = 1

End of Message: Indicates that the descriptor buffer is the last buffer in the message.

•

This bit will always be set, as this device only supports one buffer per message.

SPRUE13A – September 2006

Serial RapidIO (SRIO)

47

Submit Documentation Feedback