www.ti.com

1.3

Standards

1.4

External Devices Requirements

1.5

TI Devices Supported By This Document

Overview

Features Not Supported:

•

Compliance with the Global Shared Memory specification (GSM)

•

8/16 LP-LVDS compatible

•

Destination support of RapidIO Atomic Operations

•

Simultaneous mixing of frequencies between 1x ports (all ports must be the same frequency)

•

Target atomic operations (including increment, decrement, test-and-swap, set, and clear) for internal

L2 memory and registers

The SRIO peripheral is compliant to V1.2 of the RapidIO Interconnect Specification and V1.2 of the

RapidIO Physical Layer 1x/4x LP-Serial Specification. These and the various associated documents listed

herein can be found at the official RapidIO website:

www.RapidIO.org

.

SRIO provides a seamless interface to all devices which are compliant to V1.2 of the RapidIO Physical

Layer 1x/4x LP-Serial Specification. This includes ASIC, microprocessor, DSP, and switch fabric devices

from multiple vendors. Compliance to the specification can be verified with bus-functional models available

through the RapidIO Trade Association, as well as test suites currently available for licensing.

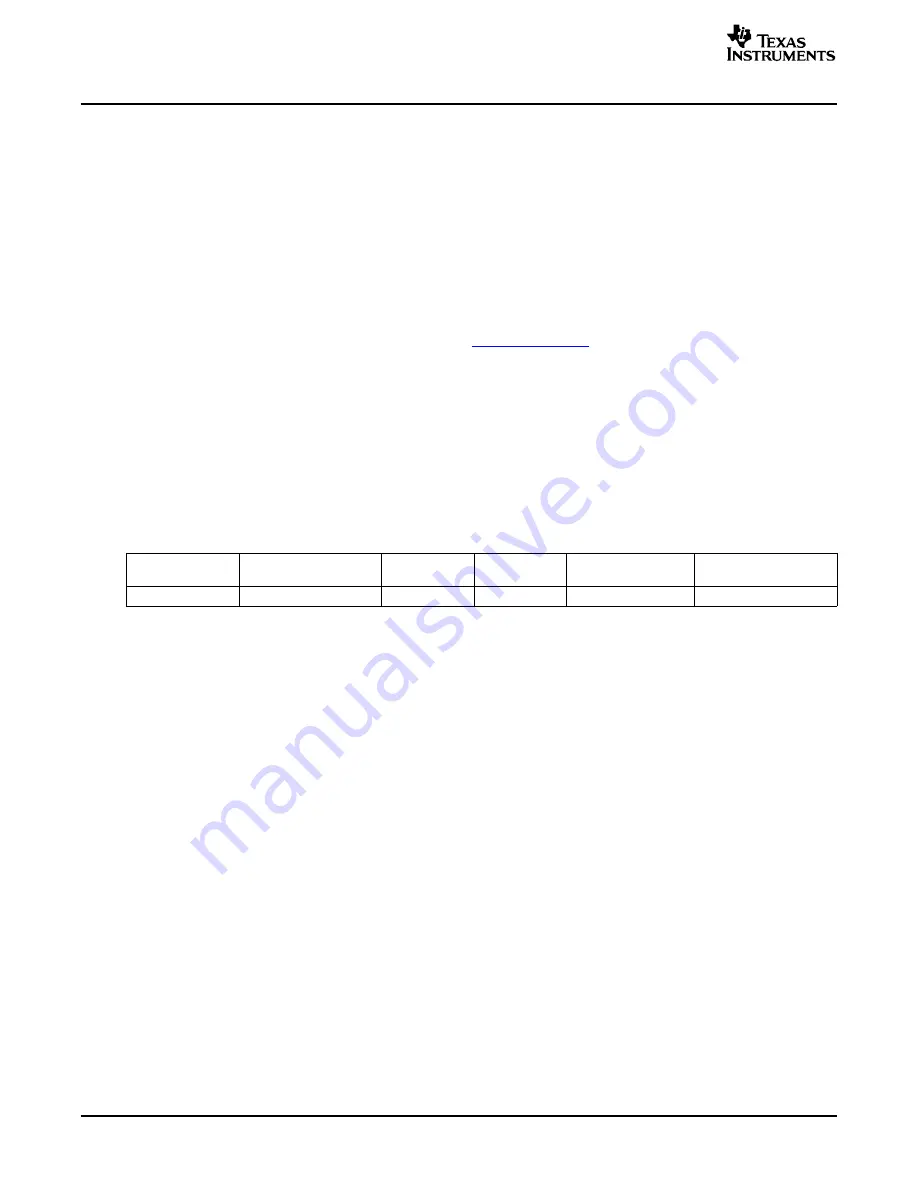

Table 1. TI Devices Supported By This Document

Number of

Number of

Number of

SRIO Module

Device

DSP Cores (CPUs)

Ports

Lanes

Configurations

Frequency

TMS320TCI6482

1

4

4

1x/4x, 1x/1x

DSP frequency

÷

4

Serial RapidIO (SRIO)

20

SPRUE13A – September 2006

Submit Documentation Feedback