MSP430xG461x

MIXED SIGNAL MICROCONTROLLER

SLAS508I − APRIL 2006 − REVISED MARCH 2011

15

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

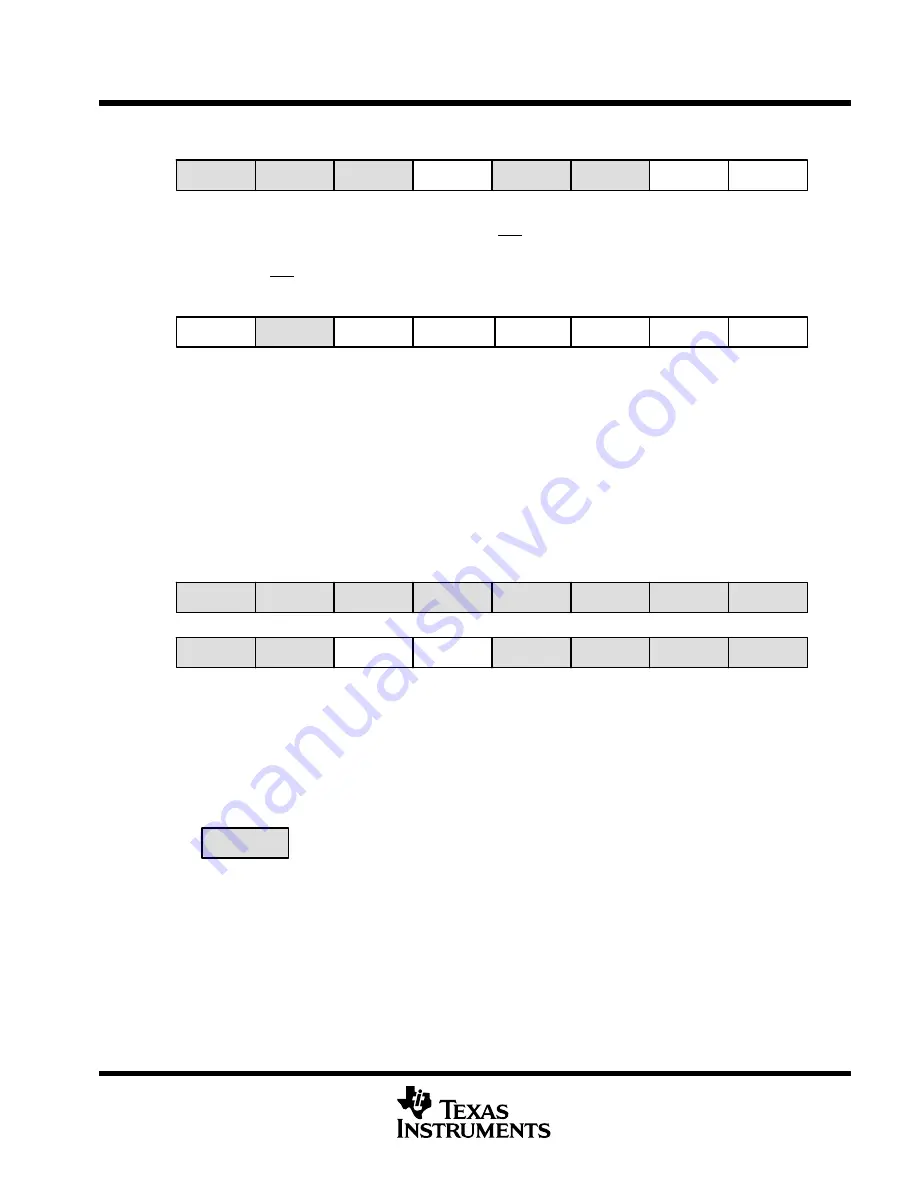

interrupt flag register 1 and 2

7

6

5

4

0

OFIFG

WDTIFG

3

2

1

rw–0

rw–1

rw–(0)

Address

02h

NMIIFG

WDTIFG:

Set on watchdog timer overflow (in watchdog mode) or security key violation

Reset on V

CC

power-on or a reset condition at the RST/NMI pin in reset mode

OFIFG:

Flag set on oscillator fault

NMIIFG:

Set via RST/NMI pin

7

6

5

4

0

3

2

1

Address

03h

BTIFG

rw–0

UTXIFG1

URXIFG1

rw–1

rw–0

UCA0TXIFG

UCA0RXIFG

rw–0

rw–0

UCB0TXIFG

UCB0RXIFG

rw–0

rw–0

UCA0RXIFG

USCI_A0 receive-interrupt flag

UCA0TXIFG

USCI_A0 transmit-interrupt flag

UCB0RXIFG

USCI_B0 receive-interrupt flag

UCB0TXIFG

USCI_B0 transmit-interrupt flag

URXIFG0:

USART1: UART and SPI receive flag

UTXIFG0:

USART1: UART and SPI transmit flag

BTIFG:

Basic timer flag

module enable registers 1 and 2

7

6

5

4

0

3

2

1

Address

04h

7

6

5

4

0

UTXE1

3

2

1

rw–0

rw–0

Address

05h

URXE1

USPIE1

URXE1:

USART1: UART mode receive enable

UTXE1:

USART1: UART mode transmit enable

USPIE1:

USART1: SPI mode transmit and receive enable

Legend

rw:

rw-0,1:

Bit can be read and written.

Bit can be read and written. It is Reset or Set by PUC.

Bit can be read and written. It is Reset or Set by POR.

rw-(0,1):

SFR bit is not present in device

Содержание MSP430CG4616IPZ

Страница 110: ......