MSP430xG461x

MIXED SIGNAL MICROCONTROLLER

SLAS508I − APRIL 2006 − REVISED MARCH 2011

99

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

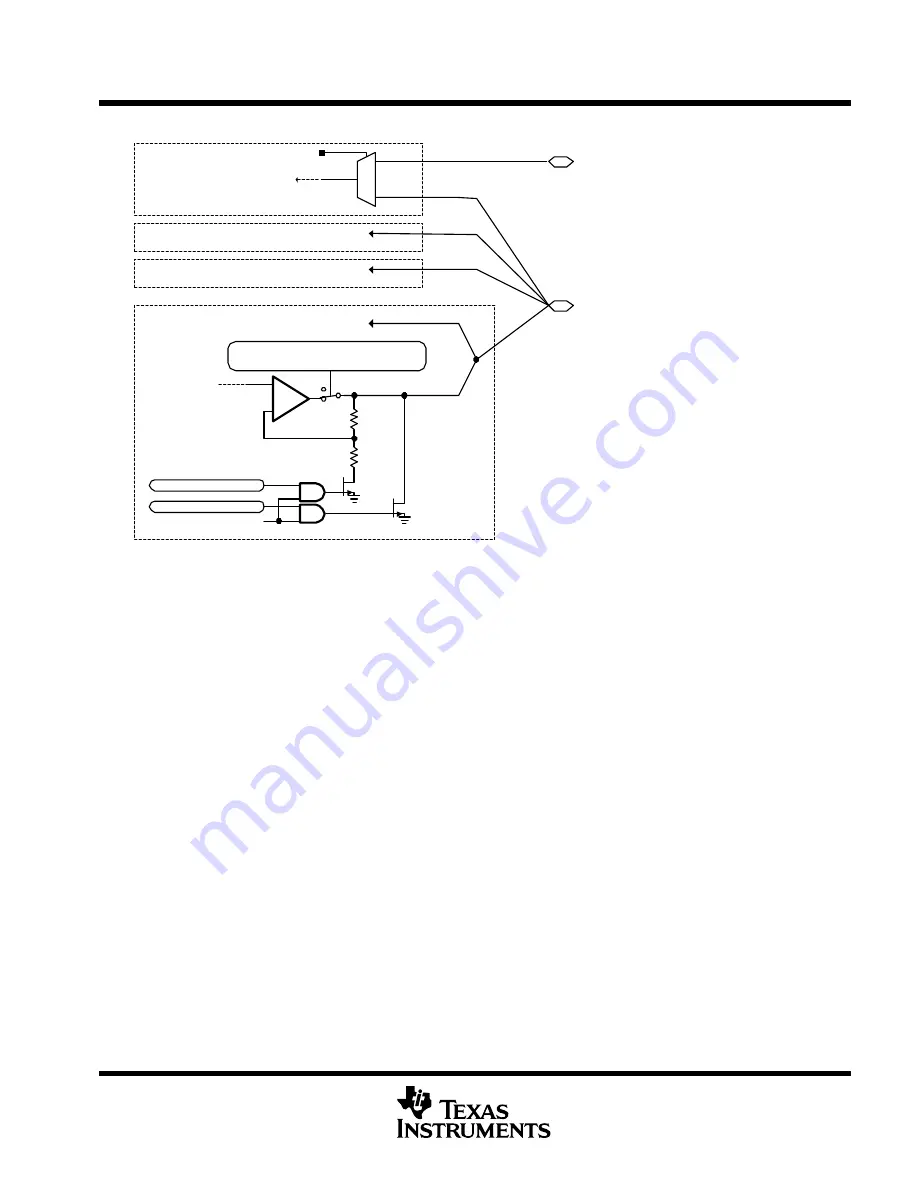

Ve

REF+

/DAC0

Ve

REF+

/DAC0

#

Reference Voltage to ADC12

1

0

’0’, if DAC12CALON = 0

DAC12AMPx>1 AND DAC12OPS=1

’1’, if DAC12AMPx=1

’1’, if DAC12AMPx>1

+

−

DAC12OPS

Reference Voltage to DAC1

Reference Voltage to DAC0

If the reference of DAC0 is taken from pin Ve

REF+

/DAC0, unpredictable voltage levels will be on pin.

In this situation, the DAC0 output is fed back to its own reference input.

#

DAC0_2_OA

DAC12.0OPS

1

0

P6.6/A6/DAC0/OA2I0

Содержание MSP430CG4616IPZ

Страница 110: ......