Interface Details

6

SPRUIE6 – April 2017

Copyright © 2017, Texas Instruments Incorporated

AMIC110 Industrial Communications Engine (AMIC110 ICE)

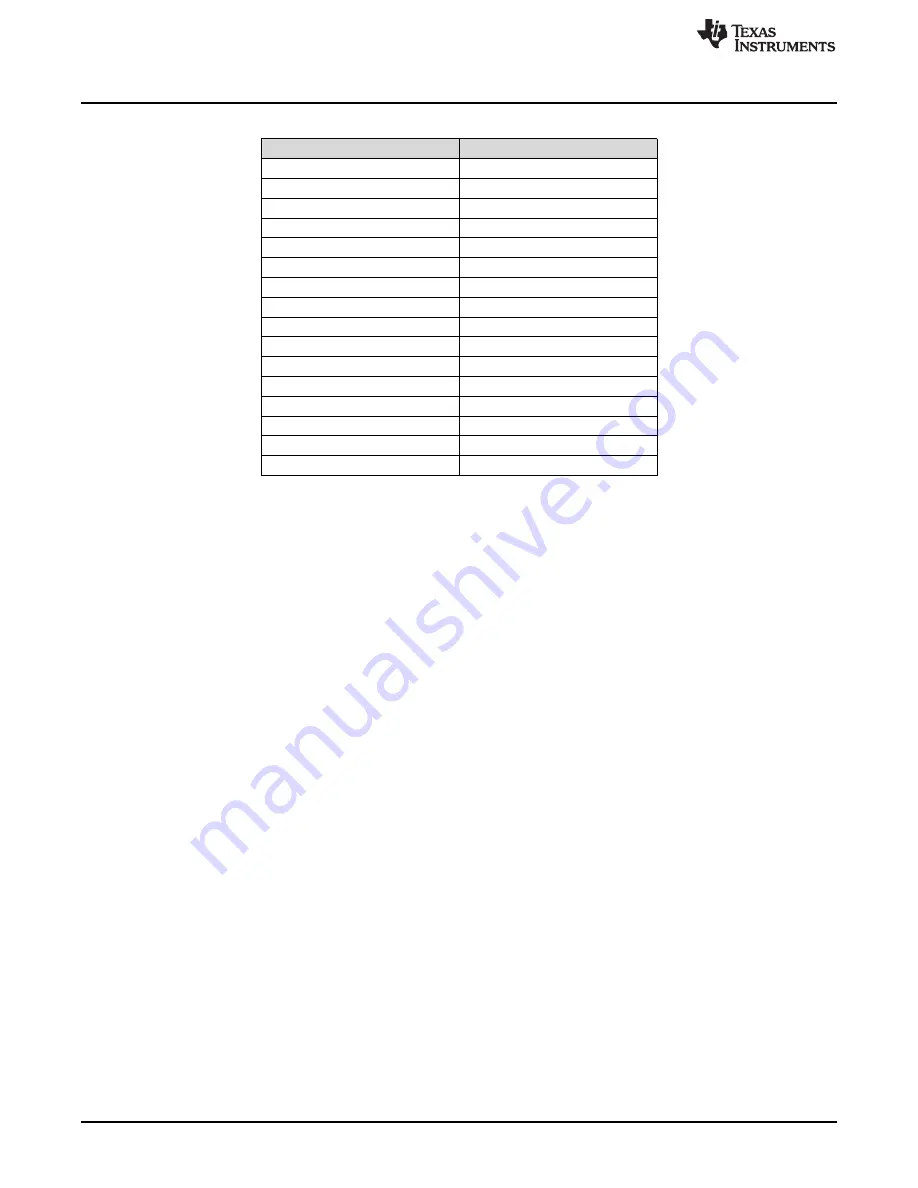

Table 1. Boot Configuration Pins

SYSBOOT Input

Resistor

15

PU

14

PD

13

PD

12

PD

11

PD

10

PD

9

PD

8

PD

7

PD

6

PD

5

PD

4

PU

3

PU

2

PD

1

PD

0

PD

2.1.1

AMIC110 Bootstrap Hardware

Several Ethernet PHY1 (U3) signals are connected to AMIC110 pins that operate as SYSBOOT inputs.

Two of the PHY1 signals must be isolated from AMIC110 SYSBOOT inputs during power on. A dual FET

switch (U10) performs this task. The switch control inputs are connected to the MII1_RXD3 pin operating

as GPIO2_18, which defaults to a high-z input with an internal pull-down after power is applied. The

internal pull-down along with an external pull-down ensures the switch is off as soon as power is applied.

The SYSBOOT buffers (U8 and U9) have an active low enable controlled by the MII1_RXD2 pin operating

as GPIO2_19, which defaults to a high-z input with an internal pull-down after power is applied. The

internal pull-down along with an external pull-down ensures the buffer is enabled as soon as power is

applied. The buffer over-drives any internal pull resistors in the Ethernet PHYs to ensure the SYSBOOT

inputs are the value defined by the SYSBOOT resistor array.

The LCD_DATA[15:0] pins are the AMIC110 SYSBOOT inputs. These pins default to high-z inputs without

any internal pull resistors turned on after power is applied. The value driven by SYSBOOT buffers will be

sampled on the rising edge of the PWRONRSTn input. These values determine the boot mode of the

AMIC110.

See the

for more details related to bootstrap hardware.