86

(c) Spectrum Instrumentation GmbH

Limits of pre trigger, post trigger, memory size

Acquisition modes

Example FIFO acquisition

The following example shows a simple FIFO single mode data acquisition setup with the read out of data afterwards. To keep this example

simple there is no error checking implemented.

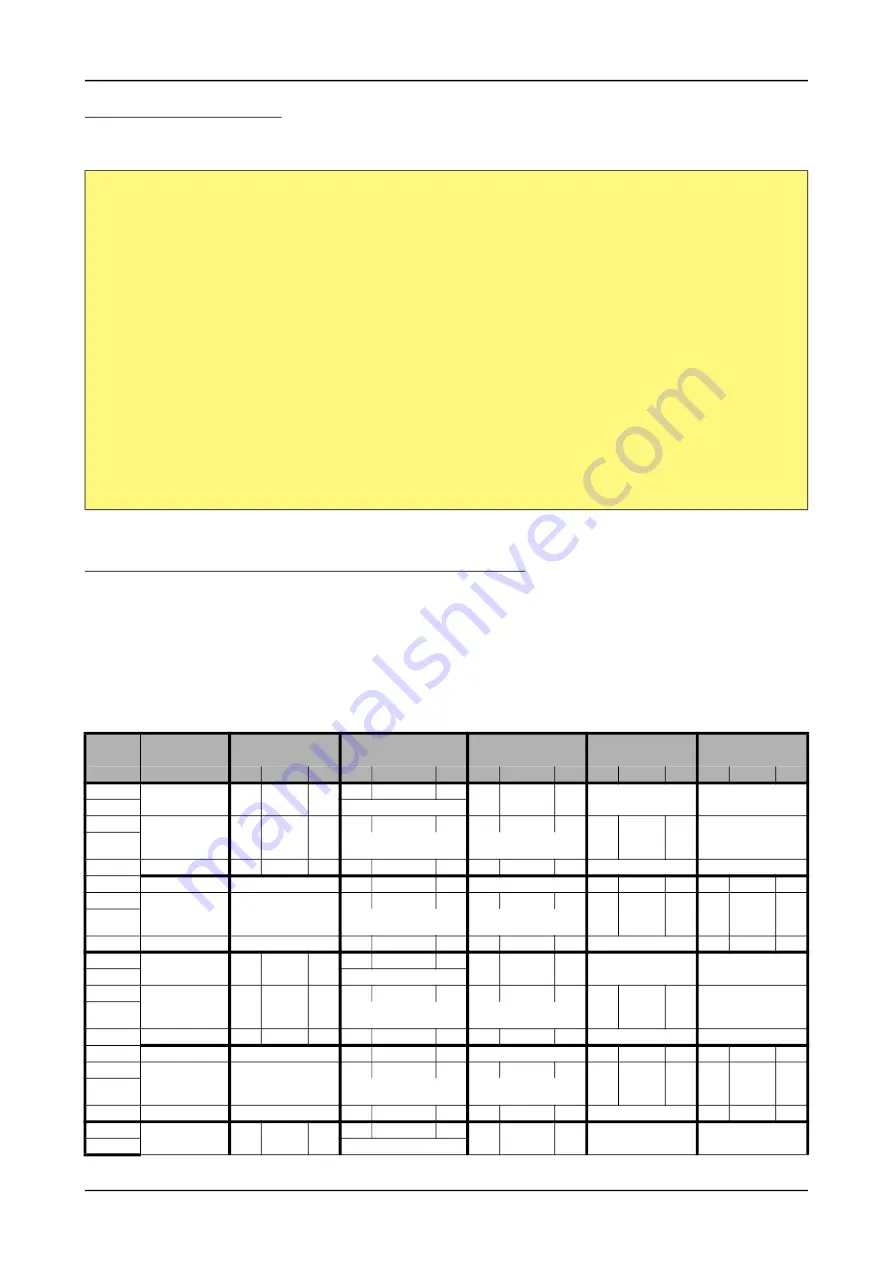

Limits of pre trigger, post trigger, memory size

The maximum memory size parameter is only limited by the number of activated channels and by the amount of installed memory. Please

keep in mind that each samples needs 2 bytes of memory to be stored. Minimum memory size as well as minimum and maximum post trigger

limits are independent of the activated channels or the installed memory.

Due to the internal organization of the card memory there is a certain stepsize when setting these values that has to be taken into account.

The following table gives you an overview of all limits concerning pre trigger, post trigger, memory size, segment size and loops. The table

shows all values in relation to the installed memory size in samples. If more memory is installed the maximum memory size figures will increase

according to the complete installed memory

spcm_dwSetParam_i32 (hDrv, SPC_CHENABLE, CHANNEL0); // only one channel activated

spcm_dwSetParam_i32 (hDrv, SPC_CARDMODE, SPC_REC_FIFO_SINGLE); // set the FIFO single recording mode

spcm_dwSetParam_i64 (hDrv, SPC_PRETRIGGER, 1024); // 1 kSample of data before trigger

// in FIFO mode we need to define the buffer before starting the transfer

void* pvData = pvAllocMemPageAligned (llBufsizeInSamples * 2); // 2 bytes per sample

spcm_dwDefTransfer_i64 (hDrv, SPCM_BUF_DATA, SPCM_DIR_CARDTOPC, 4096,

pvData, 0, 2 * llBufsizeInSamples);

// now we start the acquisition and wait for the first block

dwError = spcm_dwSetParam_i32 (hDrv, SPC_M2CMD, M2CMD_CARD_START | M2CMD_CARD_ENABLETRIGGER);

dwError = spcm_dwSetParam_i32 (hDrv, SPC_M2CMD, M2CMD_DATA_STARTDMA | M2CMD_DATA_WAITDMA);

// we acquire data in a loop. As we defined a notify size of 4k we’ll get the data in >=4k chuncks

llTotalBytes = 0;

while (!dwError)

{

spcm_dwGetParam_i64 (hDrv, SPC_DATA_AVAIL_USER_LEN, &llAvailBytes); // read out the available bytes

llTota= llAvailBytes;

// here is the right position to do something with the data (printf is limited to 32 bit variables)

printf ("Currently Available: %lld, total: %lld\n", llAvailBytes, llTotalBytes);

// now we free the number of bytes and wait for the next buffer

spcm_dwSetParam_i64 (hDrv, SPC_DATA_AVAIL_CARD_LEN, llAvailBytes);

dwError = spcm_dwSetParam_i32 (hDrv, SPC_M2CMD, M2CMD_DATA_WAITDMA);

}

Table 39: Overview of all limits of pre-trigger, post-trigger and memory size for the different channel activations and acquisition modes

Activated

Used

Memory size

Pre trigger

Post trigger

Segment size

Loops

Channels

Mode

SPC_MEMSIZE

SPC_PRETRIGGER

SPC_POSTTRIGGER

SPC_SEGMENTSIZE

SPC_LOOPS

Min

Max

Step

Min

Max

Step

Min

Max

Step

Min

Max

Step

Min

Max

Step

1 Ch

Standard Single

16

Mem

8

8

Mem - 8

8

8

8G - 8

8

not used

not used

(defined by mem and post)

Standard

Multi/ABA

16

Mem

8

8

32k

8

8

Mem - 8

8

16

Mem

8

not used

(defined by segment and

post)

(Limited by max pretrigger)

Standard Gate

16

Mem

8

8

32k

8

8

Mem - 8

8

not used

not used

FIFO Single

not used

8

32k

8

not used

16

8G - 16

8

0 (

)

4G - 1

1

FIFO Multi/ABA

not used

8

32k

8

8

8G - 8

8

16

pre+post

8

0 (

)

4G - 1

1

(defined by segment and

post)

(Limited by max pretrigger)

FIFO Gate

not used

8

32k

8

8

8G - 8

8

not used

0 (

)

4G - 1

1

2 Ch

Standard Single

16

Mem/2

8

8

Mem/2 - 8

8

8

8G - 8

8

not used

not used

(defined by mem and post)

Standard

Multi/ABA

16

Mem/2

8

8

16k

8

8

Mem/2 - 8

8

16

Mem/2

8

not used

(defined by segment and

post)

(Limited by max pretrigger)

Standard Gate

16

Mem/2

8

8

16k

8

8

Mem/2 - 8

8

not used

not used

FIFO Single

not used

8

16k

8

not used

16

8G - 16

8

0 (

)

4G - 1

1

FIFO Multi/ABA

not used

8

16k

8

8

8G - 8

8

16

pre+post

8

0 (

)

4G - 1

1

(defined by segment and

post)

(Limited by max pretrigger)

FIFO Gate

not used

8

16k

8

8

8G - 8

8

not used

0 (

)

4G - 1

1

4 Ch

Standard Single

16

Mem/4

8

8

Mem/4 - 8

8

8

8G - 16

8

not used

not used

(defined by mem and post)

Содержание M2p.59 Series

Страница 190: ......