PDP-5050SX

171

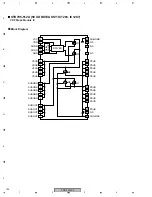

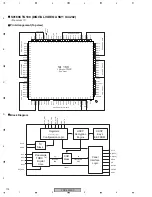

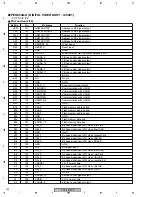

5

6

7

8

5

6

7

8

C

D

F

A

B

E

OUT46

OUT47

OUT48

OUT49

OUT50

OUT51

OUT52

OUT53

OUT54

OUT55

OUT56

OUT57

OUT58

OUT59

OUT60

OUT61

OUT62

OUT63

OUT64

NC

DDDH

DDDH

NC

GND

GND

DIR

SO

CLK

LAT

VDD

OC1

OC2

SI

CLR

GND

GND

NC

VDDH

VDDH

NC

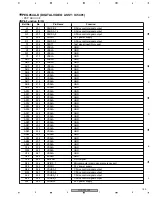

OUT1

OUT2

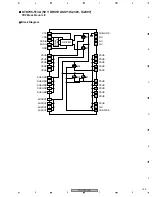

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

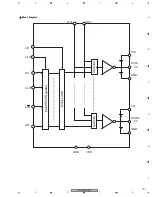

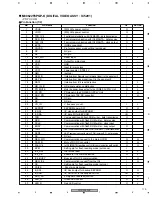

OC1

L

L

H

H

OC2

L

H

L

H

OUT

ALL Hi-Z

DATA

ALL L

ALL H

Output

High-voltage push-pull output pin

Output

High-voltage push-pull output pin

Output

High-voltage push-pull output pin

-

Not connected

-

Not connected

-

Not connected

-

Not connected

Ground

GND pin

Ground

GND pin

Ground

GND pin

Ground

GND pin

Supply

High-voltage circuit supply pin

Supply

High-voltage circuit supply pin

Supply

High-voltage circuit supply pin

Supply

High-voltage circuit supply pin

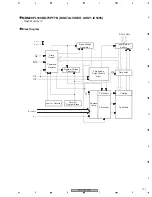

SI

Input/OutputSerial data input/output pin

Pin No.

Pin Name

Type

Discription

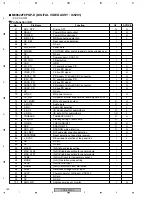

Output control pin

Input

Control output according to the right truth value table

Supply

Logic supply pin

LAT data input pin

L: Transfer shft register data to output latch

H: Hold data to output latch

Input

Input

Input

Input

Serial clock input pin

Fetch SI or SO data to sift register by CLK rise edge

Serial data input/output pin

Setup pin of sift register sift direction

L: Shift into reverse (SO

=

SI)

H: Shift forward (SI

=

SO)

All output reset pin

CLR pin: L

=

Normal operation

CLR pin: H

=

All output High

Pin Function (2/2)

Содержание PDP4350SX

Страница 9: ...PDP 5050SX 9 5 6 7 8 5 6 7 8 C D F A B E ...

Страница 51: ...PDP 5050SX 51 5 6 7 8 5 6 7 8 C D F A B E ...