EN 49

3139 785 33120

8.

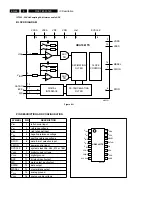

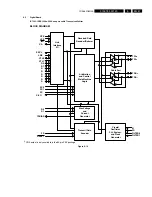

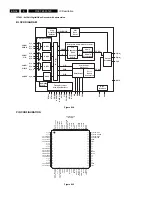

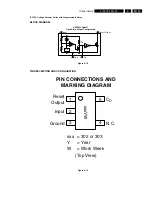

IC description

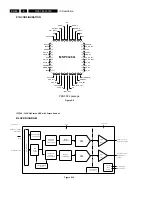

PIN DESCRIPTION

TERMINAL

TYPE

I/O

DESCRIPTION

PHP NO.

TYPE

I/O

DESCRIPTION

26, 32, 36

Supply

–

Analog circuit ground terminals. These terminals should be tied together to the

low-impedance circuit board ground plane.

25, 35

Supply

–

Analog circuit power terminals. A combination of high frequency decoupling

capacitors near each terminal is suggested, such as paralleled 0.1

µ

F and 0.001

µ

F. Lower frequency 10

µ

F filtering capacitors are also recommended. These

supply terminals are separated from PLLVDD and DVDD inside the device to provide

noise isolation. They should be tied at a low-impedance point on the circuit board.

15

CMOS

I/O

Bus manager contender programming input and link-on output. On hardware reset,

this terminal is used to set the default value of the contender status indicated during

self-ID. Programming is done by tying the terminal through a 10-k

Ω

resistor to a high

(contender) or low (not contender). The resistor allows the link-on output to override

the input. However, it is recommended that this terminal should be programmed

low, and that the contender status be set via the C register bit.

If the TSB41AB1 is used with an LLC that has a dedicated terminal for monitoring

LKON and also setting the contender status, then a 1-k

Ω

series resistor should be

placed on the LKON line between the PHY and LLC to prevent bus contention.

Following hardware reset, this terminal is the link-on output, which is used to notify

the LLC to power up and become active. The link-on output is a square-wave signal

with a period of approximately 163 ns (8 SYSCLK cycles) when active. The link-on

output is otherwise driven low, except during hardware reset when it is

high-impedance.

The link-on output is activated if the LLC is inactive (LPS inactive or the LCtrl bit

cleared) and when:

a) the PHY receives a link-on PHY packet addressed to this node, or

b) the PEI (port-event interrupt) register bit is 1, or

c) any of the CTOI (configuration-time-out interrupt), CPSI

(cable-power-status interrupt), or STOI (state-time-out

interrupt) register bits are 1 and the RPIE (resuming-port

interrupt enable) register bit is also 1.

Once activated, the link-on output continues active until the LLC becomes active

(both LPS active and the LCtrl bit set). The PHY also deasserts the link-on output

when a bus reset occurs unless the link-on output would otherwise be active

because one of the interrupt bits is set (that is, the link-on output is active due solely

to the reception of a link-on PHY packet).

NOTE: If an interrupt condition exists which would otherwise cause the link-on

output to be activated if the LLC were inactive, the link-on output is activated when

the LLC subsequently becomes inactive.

N/A

CMOS

O

Cable-not-active output. This terminal is asserted high when there is no incoming

bias voltage.

20

CMOS

I

Cable power status input. This terminal is normally connected to cable power

through a 400-k

Ω

resistor. This circuit drives an internal comparator that is used to

detect the presence of cable power. This terminal should be tied directly to DVDD

supply if application does not require it to be used.

2

3

CMOS

I/O

Control I/Os. These bidirectional signals control communication between the

TSB41AB1 and the LLC. Bus holders are built into these terminals.

NAME

AGND

AVDD

C/LKON

CNA

CPS

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

4

5

6

7

8

9

10

11

CMOS

I/O

Data I/Os. These are bidirectional data signals between the TSB41AB1 and the

LLC. Bus holders are built into these terminals.