NAT-MCH Clock-PCB – Technical Reference Manual

Version 1.4

© N.A.T. GmbH

46

11.3.20

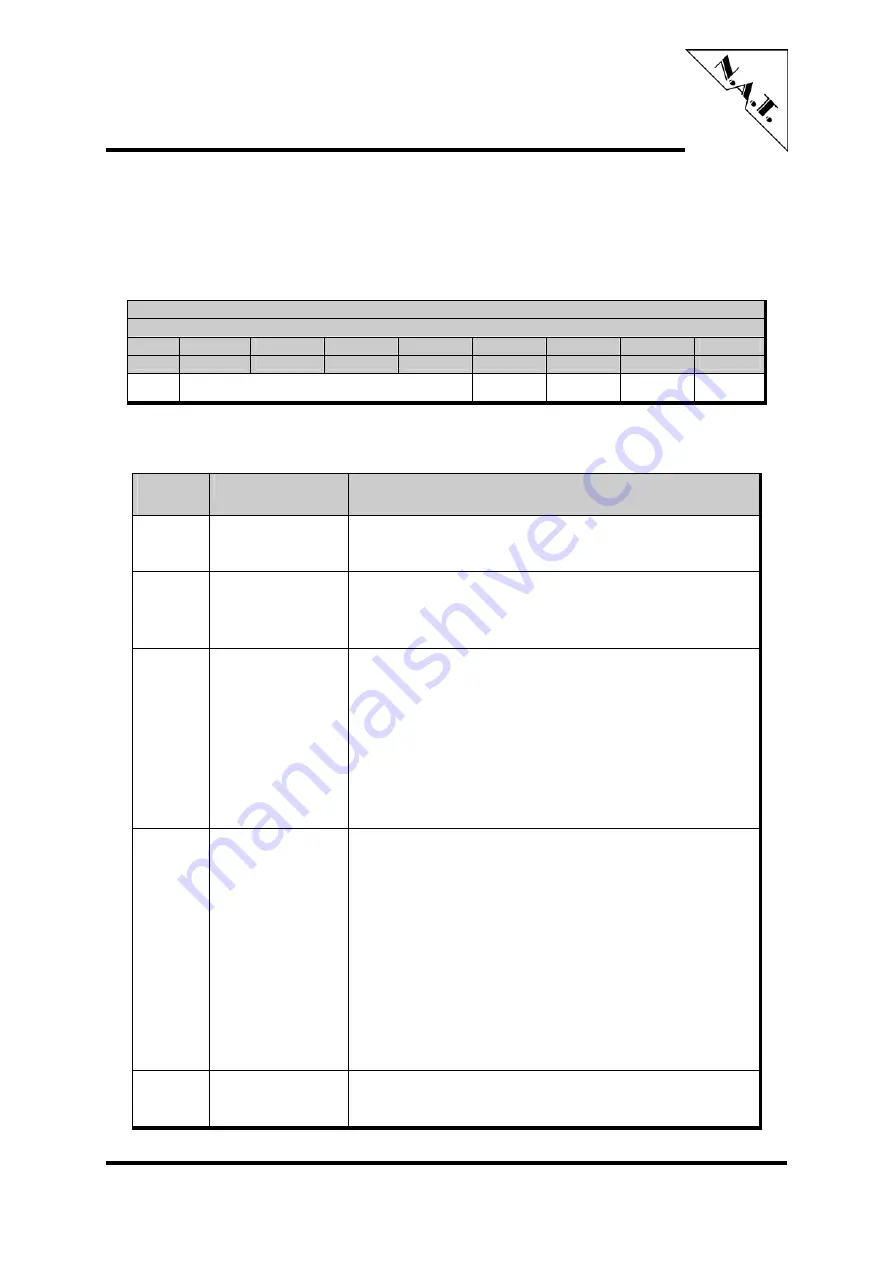

PLL Control 2 Register

The PLL Control 2 Register manages together with the PLL_CTR1 Register the control

inputs of the Zarlink PL L.

Table 41:

PLL_CTR2 Register

PLL Control 2 - Address 0x13

Default value 0x00

Bit

7

6

5

4

3

2

1

0

Access

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Func - HMS

SEC_

MSTR

TIE_

CLEAR

FAST-

LOCK

Table 42:

PLL_CTR2 - Register Bits

Bit

Name

Function

0

FAST-

LOCK

set temporarily high to allow the PLL to quickly lock

to the input reference (one second locking time)

1

TIE_

CLEAR

A logic low at this input resets the Time Interval Error

(TIE) correction circuit resulting in a realignment of

input phase with output phase.

2

SEC_MSTR

Clearing this bit selects the Primary Master mode of

operation with 1.8 Hz or 3.6 Hz DPLL loop filter

bandwidth.

Setting this bit selects Secondary Master mode which

forces the PLL to clear its TIE corrector circuit and

lock to the selected reference using a high bandwidth

loop filter and a phase slope limiting of 9.5 ms/s.

3

HMS

The HMS input controls phase accumulation during the

transition from Holdover or Freerun mode to Normal

mode on the same reference.

A logic low at this bit will cause the PLL to maintain

the delay stored in the TIE corrector circuit when it

transitions from Holdover or Freerun mode to Normal

mode. A 1 on this bit will cause the PLL to measure a

new delay for its TIE corrector circuit thereby

minimizing the output phase movement when it

transitions from Holdover or Freerun mode to Normal

mode.

[7..4]

-

no function

write as 0 and ignore when read