3-40

Computer Group Literature Center Web Site

PCCchip2

3

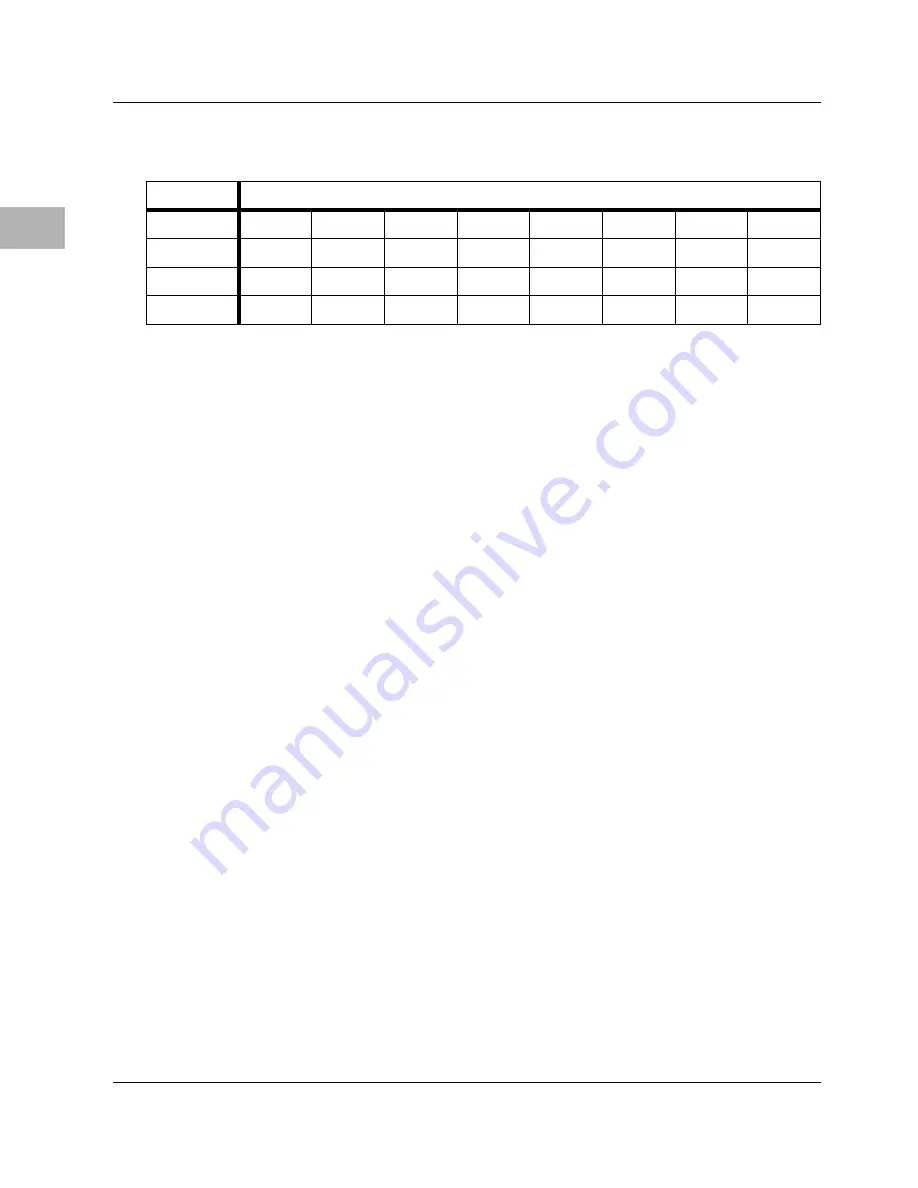

Printer FAULT Interrupt Control Register

IL2-IL0

These three bits select the interrupt level for the printer

FAULT. Level 0 does not generate an interrupt.

ICLR

In edge-sensitive mode, writing a logic 1 to this bit clears

the INT status bit. This bit has no function in level-

sensitive mode. This bit is always read as zero.

IEN

When this bit is high, the interrupt is enabled. The

interrupt is disabled when this bit is low.

INT

When this bit is high, a printer FAULT interrupt is being

generated at the level programmed in IL2-IL0 (if

nonzero).

E/L*

When this bit is high, the interrupt is edge-sensitive. The

interrupt is level-sensitive when this bit is low.

PLTY

When this bit is low, interrupt is activated by a falling

edge/low level of the PRFAULTI* pin.

When this bit is high, interrupt is activated by a rising

edge /high level of the PRFAULTI* pin.

Note that if this bit is changed while the E/L* bit is set (or

is being set), a FAULT interrupt may be generated. This

can be avoided by setting the ICLR bit during write cycles

that change the E/L* bit.

ADR/SIZ

$FFF42031 (8 bits)

BIT

23

22

21

20

19

18

17

16

NAME

PLTY

E/L*

INT

IEN

ICLR

IL2

IL1

IL0

OPER

R/W

R/W

R

R/W

C

R/W

R/W

R/W

RESET

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL

Содержание MVME1X7P

Страница 1: ...MVME1X7P Single Board Computer Programmer s Reference Guide V1X7PA PG1 Edition of October 2000 ...

Страница 16: ...xvi ...

Страница 18: ...xviii ...

Страница 20: ...xx ...

Страница 26: ...xxvi ...

Страница 90: ...1 64 Computer Group Literature Center Web Site Programming Issues 1 ...

Страница 248: ...3 50 Computer Group Literature Center Web Site PCCchip2 3 ...

Страница 286: ...4 38 Computer Group Literature Center Web Site MCECC Functions 4 ...

Страница 288: ...A 2 Computer Group Literature Center Web Site Summary of Changes A ...

Страница 316: ...Index IN 14 Computer Group Literature Center Web Site I N D E X ...