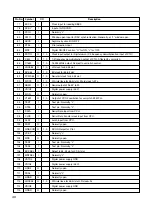

40

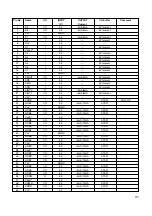

Pin No.

Symbol

I/O

Description

77

EXCK

I

Clock input for reading SBS0

78

SCSY

I

Input of G RSCOR.

79

VCOI

I

Normally “L”

80

XWO

I

Window open input for DAC synchronization. Generally, at “L” window open

81

ASYE

I

Asymmetry circuit ON/OFF

82

XTSL

I

X’tal selection input

83

MD2

I

Digital ON/OFF control. “H” for ON, “L” for OFF.

84

FSTIO

O

1, 0

Clock input/output for Digital servo (2/3 frequency demultiplication input of XTLI)

85

C4M

O

1, 0

1/4 frequency demultiplication output of XTLI. Affected by vari-pitch.

86

C16M

O

1, 0

16,9344MHz output. Subject to vari-pitch control.

87

LRCK64

O

1, 0

LR clock for 64-bit slot

88

BCK64

O

1, 0

Bit clock for 64-bit slot

89

PCMD64

O

1, 0

Serial bit clock for 64-bit slot

90

WDCK

O

1, 0

D/A interface for 48-bit slot. Word clock f=2Fs.

91

SBSO

O

1, 0

Serial output of Sub P to W.

92

VDIO2

Digital power supply (3.3V)

93

MON

O

Normally open.

94

V16M

O

1, 0

Output of VCO2 oscillation for vari-pitch EFM PLL.

95

TEST

I

Test pin. Normally “L”.

96

DTS0

I

Test pin. Normally “L”.

97

DATA

I

Serial Data input from CPU.

98

CLCK

I

Serial Data transfer clock input from CPU.

99

XLAT

I

Latch input from CPU.

100

FSW

O

Normally open.

101

GRSCOR

O

1, 0

SCOR Output for X’tal.

102

VCKT

I

Normally “L”

103

MDS

O

Normally open.

104

TES2

I

Test pin. Normally “L”

105

TES3

I

Test pin. Normally “L”

106

BCKSEL

I

Select to 48-bit slot or 32-bit slot

107

MNTSEL

I

Normally “L”

108

VSTO3

Digital power supply GND

109

VDIO4

Digital power supply (3.3V)

110

HDBF

O

Normally open.

111

PSSL

I

Normally "L"

112

HDBE

O

Normally open.

113

LRCK48

O

1, 0

D/A interface for 48-bit slot LR clock=Fs

114

VSIO5

Digital power supply GND

115

HDBD

O

Normally open