88

Keysight M8132A 640 GSa/s Digital Signal Processor User’s Guide

6

Remote Programming

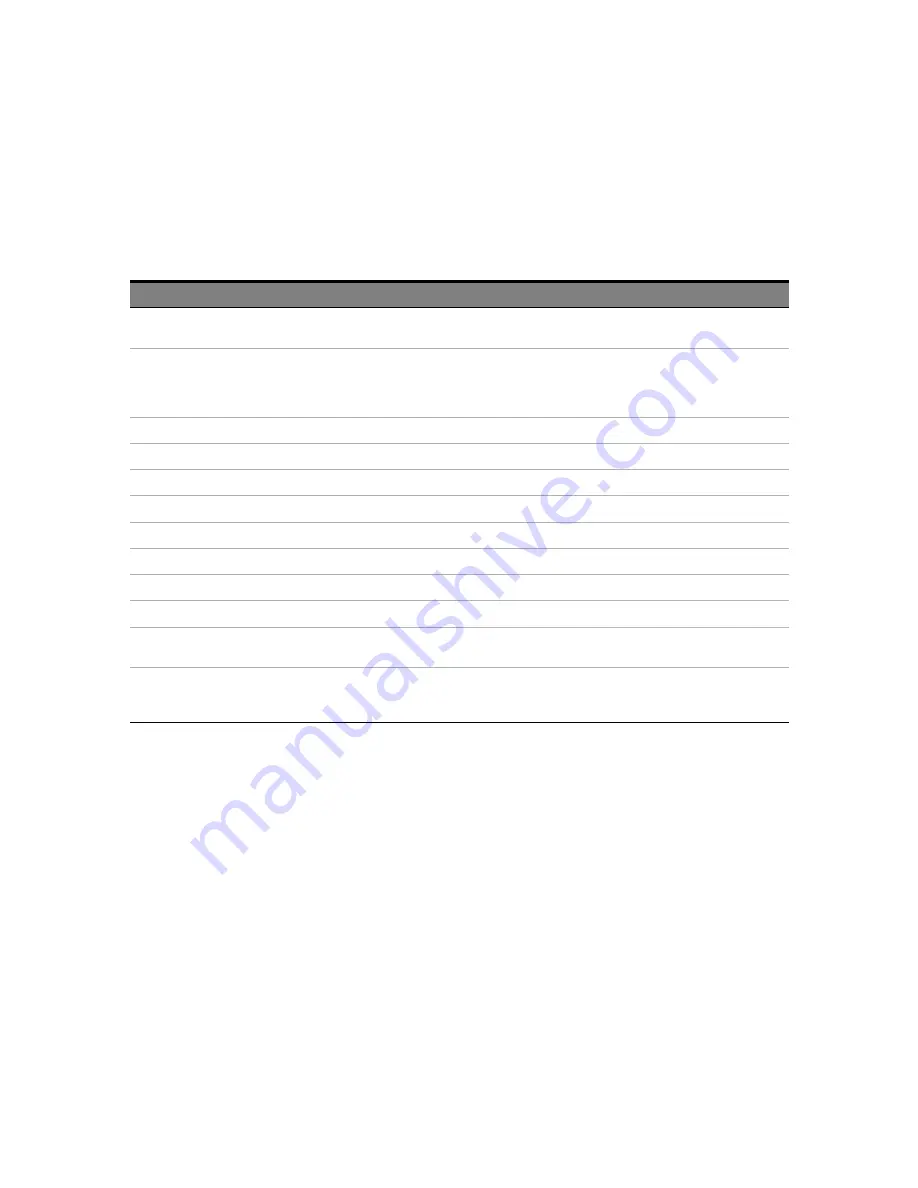

Table 12

Status bits described with “since last GetStatus” are cleared by

:ODI:PORT<N>:CSTatus?

query. All status bits will be 0 on an inactive

port.

Name

Bits

Description

Active

0

Port activated by software. Actual readiness to send and receive will depend upon the opposite

end of the link and flow control configuration.

TxReady

1

Ready to transmit and flow control allows. If flow control is disabled, transmit will always be

ready to send. If flow control is enabled, the port will not be ‘ready to send’ until receiver is ready

and indicating XON via flow control. To troubleshoot TxReady not becoming set in this case,

troubleshoot the receive path starting with RxSignalLoss.

RxReady

2

Receiver ready. All lanes synchronized and aligned.

RxLaneError

3

Error in one or more lanes since last GetStatus.

RxBurstMaxError

4

Received too large a burst since last GetStatus.

RxCrcError

5

Received bad burst CRC since last GetStatus.

RxOverrun

6

Receiver data overrun since last GetStatus

RxSignalLoss

7

Received signal loss. Optical power too low.

RxSyncPending

8

Receiver activated but has not achieved synchronization

9 to 15

Unused

RxFcStatus

16

Received link-level flow control status. 1 is XON, 0 is XOFF. From Interlaken idle/control word bit

55 or from an out-of-band flow control signal.

RxFcStatus0

to

RxFcStatus14

17

to

31

Received per-channel flow control status bits. 1 is XON, 0 is XOFF. Bit 17 is channel 0 from bit

54 of the Interlaken idle/control word, bit 18 is channel 1 from bit 53 of the control word, and so

on.

Содержание M8132A

Страница 1: ...User s Guide Keysight M8132A 640 GSa s Digital Signal Processor...

Страница 8: ......

Страница 16: ......

Страница 22: ......

Страница 46: ......

Страница 48: ......

Страница 94: ......

Страница 102: ......

Страница 106: ...This information is subject to change without notice Keysight Technologies 2020 Edition 2 0 May 2020 www keysight com...