RC-BM5

1-23

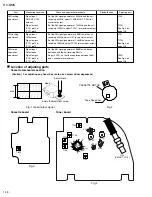

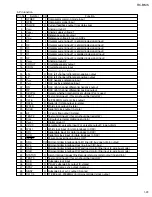

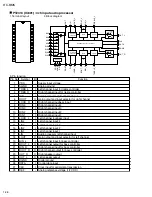

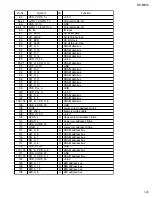

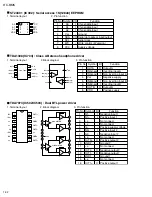

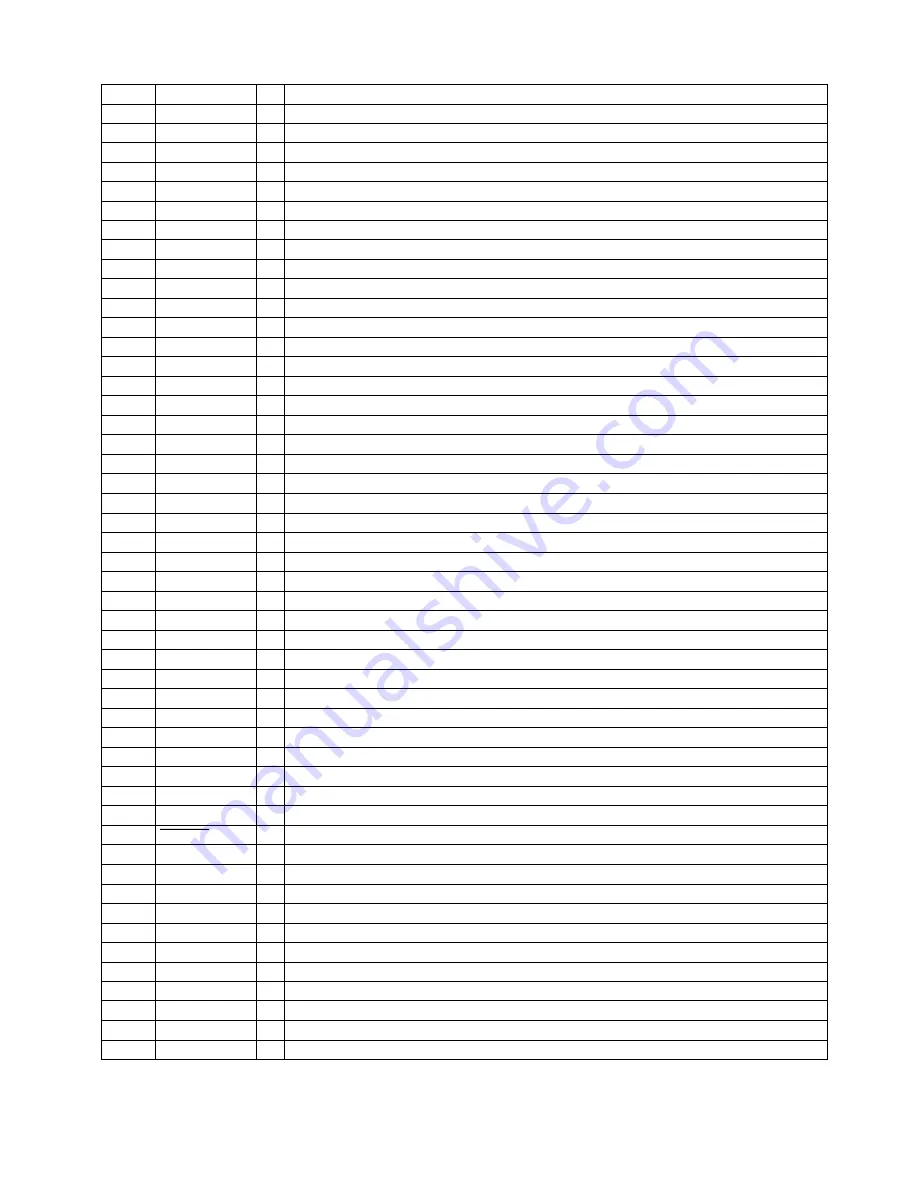

3. Pin function

Pin No.

Symbol

I/O

Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

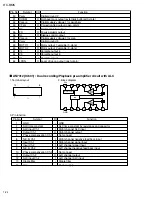

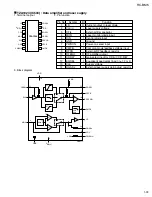

HFREF

HFIN

ISLICE

V

SSA1

V

DDA1

Iref

V

RIN

D1

D2

D3

D4

R1

R2

V

SSA2

CROUT

CRIN

V

DDA2

LN

LP

V

neg

V

pos

RN

RP

SELPLL

TEST1

CL16

DATA

WCLK

SCLK

EF

TEST2

KILL

V

SSD1

V2/V3

WCLI

SDI

SCLI

RESET

SDA

SCL

RAB

SILD

STATUS

TEST3

RCK

SUB

SFSY

SBSY

CL11/4

I

I

O

-

-

O

-

I

I

I

I

I

I

-

O

I

-

O

O

I

I

O

O

-

I

O

O

O

O

O

I

O

-

I/O

I

I

I

I

I/O

I

I

I

O

I

I

O

O

O

O

Comparator common mode input

Comparator signal input

Current feedback output from data slicer

Analog ground 1

Analog supply voltage 1

Reference current output

Reference voltage for servo ADCs

Unipolar current input 1 (central diode signal input)

Unipolar current input 2 (central diode signal input)

Unipolar current input 3 (central diode signal input)

Unipolar current input 4 (central diode signal input)

Unipolar current input 1 (satellite diode signal input)

Unipolar current input 2 (satellite diode signal input)

Analog ground 2

Crystal/resonator output

Crystal/resonator input

Analog supply voltage 2

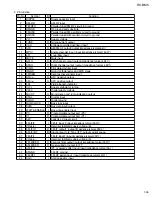

DAC left channel differential negative output

DAC left channel differential positive output

DAC negative reference input

DAC positive reference input

DAC right channel differential negative output

DAC right channel differential positive output

Selects whether internal clock multiplier PLL is used

Test control input 1 (this pin should be tied LOW)

16.9344MHz system clock output

Serial d4(1) data output (3-state)

Word clock output (3-state)

Serial bit clock output (3-state)

C2 error flag output (3-state)

Test control input 2 (this pin should be tied LOW)

Kill output (programmable;open-drain)

Digital ground 1

Versatile I/O:versatile input 2 or versatile output 3 (open-drain)

Word clock input (for data loopback to DAC)

Serial data input (for data loopback to DAC)

Serial bit clock input (for data loopback to DAC)

Power-on reset input (active LOW)

Microcontroller interface data I/O line (IIC-bus;open-drain output)

Microcontroller interface clock line input (IIC-bus)

Microcontroller interface R/W and load control line input (4-wire bus mode)

Microcontroller interface R/W and load control line input (4-wire bus mode)

Servo interrupt request line/decoder status register output (open-drain)

Test control input 3 (this pin should be tied LOW)

Subcode clock input

P-to-W subcode bits output (3-states)

Subcode frame sync output (3-sates)

Subcode block sync output (3-sates)

11.2896 or 4.2336MHz (for microcontroller) clock output

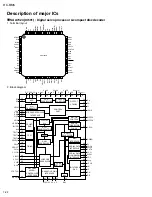

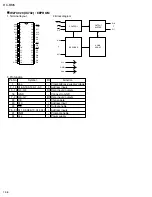

Содержание RC-BM5

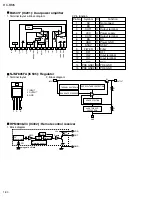

Страница 41: ...RC BM5 2 1 A B C D E F G 1 2 3 4 5 Block diagram ...

Страница 48: ...RC BM5 2 8 RC BM5 H A B C D E F G 1 2 3 4 5 Printed circuit boards Main board Reverse side ...

Страница 49: ...RC BM5 2 9 A B C 1 2 3 4 5 Tuner board Cassette board Reverse side Reverse side ...

Страница 50: ...RC BM5 2 10 A B C D 1 2 3 4 5 Display board Reverse side Power amplifier board Reverse side ...

Страница 51: ...RC BM5 2 11 A B C 1 2 3 4 5 Volume switch board Reverse side Phone jack board Reverse side ...