Intel® 460GX Chipset Software Developer’s Manual

16-5

IFB Power Management

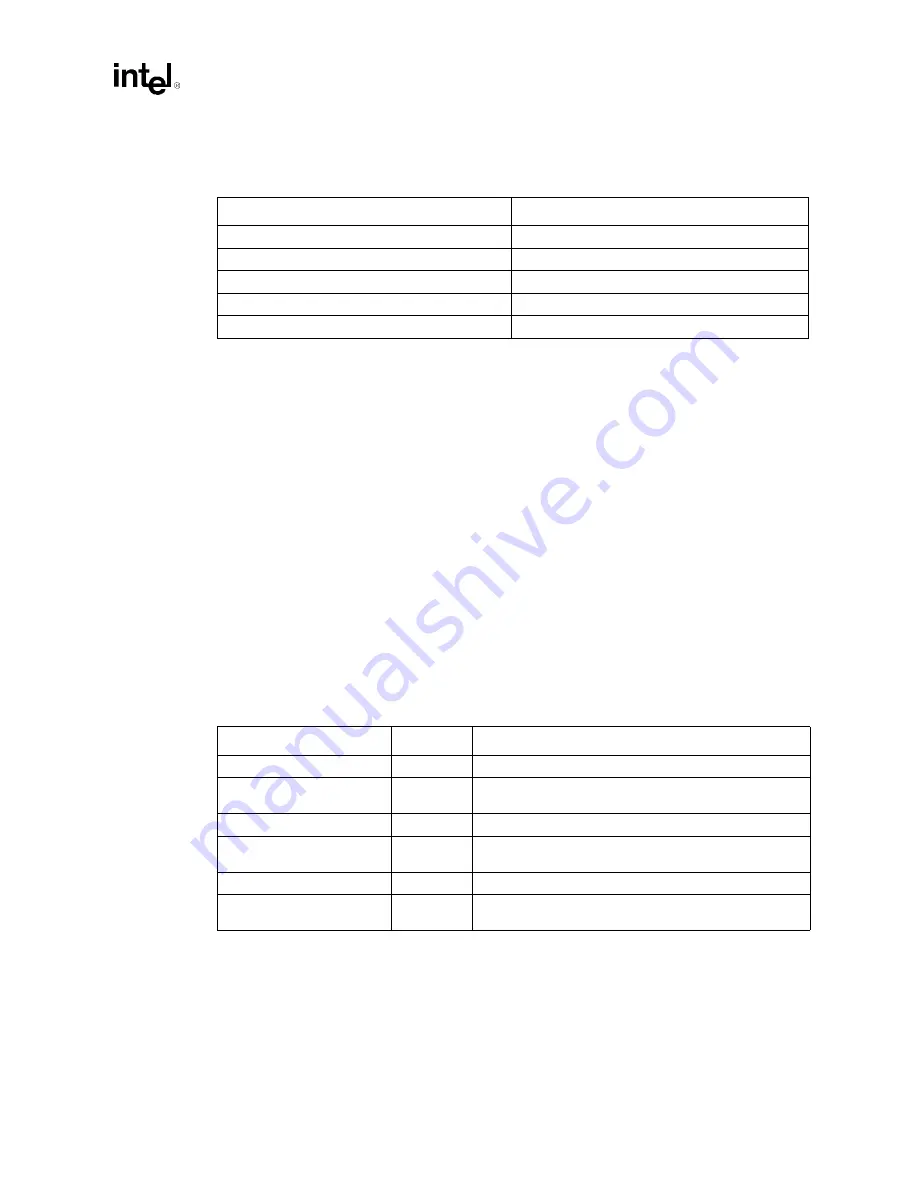

A Wake event will cause an exit from the Soft-Off state. The wake events that can wake from the

S5 state are:

16.3

Handling of Power Failures in IFB

A power failure is defined as any one of the following:

•

PWROK goes low and the IFB did not yet cause SUSB and/or SUSC to go inactive.

•

Power to the Resume plane (as detected by RSMRST# or Vcc

RESUME

) goes inactive.

Upon detection of a power failure, the state machine will go to the G3 state and the IFB will set a

new status bit called PWR_FAIL. That bit can be cleared only by writing a 1 to that bit position.

Add new config bit, AFTERG3, powered off RTC well to indicate what should be done after power

failure:

•

1 = Return to S4/S5 state (see table below), 0 = Cold Boot.

•

Software should set this bit prior to going to an S4 or S5 state if it desires the system to return

there after the power failure. This bit is automatically set to 1 due to a Power Button Override

event.

When RSMRST# (or the Resume Vcc) is inactive after a power failure, the state machine will

transition based on the following table:

If USB devices are attached, setting the AFTERG3 bit to 1 may not be a good idea, since the USB

devices will lose their configuration during the power failure and may no longer be able to generate

a wake events when the power is restored. In this case, the system may have to always boot after a

power failure (except if placed into the S5 state due to Power Button Override).

S5 Wake Event

Comment

RTC Alarm cause RTC_STS bit set

RTC_EN must be set for the wake event

Power button press causes PWRBTN_STS bit set

Power Button is unconditional wake event

Ring Indicate causes RI_STS bit set

RI_EN must be set for the wake event

GPIO Routed to SCI goes active

EXTSCI_EN must be set for the wake event

GPIO Routed to SMI goes active

EXTSMI_EN must be set for the wake event

State Prior to Power Failure

AFTERG3

Action after Power Returns

S0, S1

0

Cold boot to return to S0 state. SUSB and SUSC go inactive.

S0, S1

1

No boot. SUSB and SUSC stay active (S5 state) until wake

event.

S4

0

Cold boot to return to S0 state. SUSB and SUSC go inactive.

S4

1

No boot. SUSB and SUSC stay active (S4 state) until wake

event.

S5

0

Cold boot to return to S0 state. SUSB and SUSC go inactive.

S5

1

No boot. SUSB and SUSC stay active (S5 state) until wake

event.

Содержание 460GX

Страница 1: ...Intel 460GX Chipset System Software Developer s Manual June 2001 Document Number 248704 001 ...

Страница 20: ...Introduction 1 8 Intel 460GX Chipset Software Developer s Manual ...

Страница 80: ...System Architecture 3 8 Intel 460GX Chipset Software Developer s Manual ...

Страница 90: ...System Address Map 4 10 Intel 460GX Chipset Software Developer s Manual ...

Страница 98: ...Memory Subsystem 5 8 Intel 460GX Chipset Software Developer s Manual ...

Страница 146: ...AGP Subsystem 7 16 Intel 460GX Chipset Software Developer s Manual ...

Страница 170: ...IFB Register Mapping 9 6 Intel 460GX Chipset Software Developer s Manual ...

Страница 190: ...IFB Usage Considerations 10 20 Intel 460GX Chipset Software Developer s Manual ...

Страница 232: ...LPC FWH Interface Configuration 11 42 Intel 460GX Chipset Software Developer s Manual ...

Страница 244: ...IDE Configuration 12 12 Intel 460GX Chipset Software Developer s Manual ...

Страница 258: ...Universal Serial Bus USB Configuration 13 14 Intel 460GX Chipset Software Developer s Manual ...

Страница 270: ...SM Bus Controller Configuration 14 12 Intel 460GX Chipset Software Developer s Manual ...

Страница 288: ...PCI LPC Bridge Description 15 18 Intel 460GX Chipset Software Developer s Manual ...

Страница 294: ...IFB Power Management 16 6 Intel 460GX Chipset Software Developer s Manual ...