C141-E034-02EN

4 - 14

(4)

Viterbi detection circuit

The sample hold waveform output from the adaptive equalizer circuit is sent to the Viterbi

detection circuit. The Viterbi detection circuit demodulates data according to the survivor path

sequence.

(5)

Data separator circuit

The data separator circuit generates clocks in synchronization with the output of the adaptive

equalizer circuit. To write data, the VFO circuit generates clocks in synchronization with the clock

signals from a synthesizer.

(6)

8/9 GCR decoder

This circuit converts the 9-bit read data into the 8-bit NRZ data.

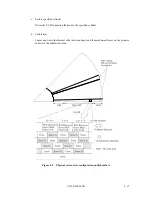

4.6.4

Time base generator circuit

The drive uses constant density recording to increase total capacity. This is different from the

conventional method of recording data with a fixed data transfer rate at all data area. In the

constant density recording method, data area is divided into zones by radius and the data transfer

rate is set so that the recording density of the inner cylinder of each zone is nearly constant. The

drive divides data area into 15 zones to set the data transfer rate. Table 4.3 describes the data

transfer rate and recording density (BPI) of each zone.

Содержание MPA3017AT

Страница 1: ...C141 E034 02EN MPA3017AT MPA3026AT MPA3035AT MPA3043AT MPA3052AT DISK DRIVES PRODUCT MANUAL ...

Страница 29: ...C141 E034 02EN 3 2 Figure 3 1 Dimensions ...

Страница 44: ...C141 E034 02EN 4 5 Figure 4 2 MPA30xxAT Block diagram ...

Страница 50: ...C141 E034 02EN 4 11 Figure 4 4 Read write circuit block diagram ...

Страница 52: ...C141 E034 02EN 4 13 Figure 4 6 PR4 signal transfer ...