C141-E034-02EN

4 - 3

4.2.3

Spindle

The spindle consists of a disk stack assembly and spindle motor. The disk stack assembly is

activated by the direct drive sensor-less DC spindle motor, which has a speed of 5,400 rpm ±0.5%.

The spindle is controlled with detecting a PHASE signal generated by counter electromotive

voltage of the spindle motor at starting. After that, the rotational speed is kept with detecting a

servo information.

4.2.4

Actuator

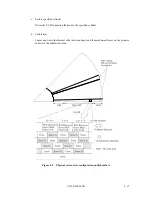

The actuator consists of a voice coil motor (VCM) and a head carriage. The VCM moves the head

carriage along the inner or outer edge of the disk. The head carriage position is controlled by

feeding back the difference of the target position that is detected and reproduced from the servo

information read by the read/write head.

4.2.5

Air filter

There are two types of air filters: a breather filter and a circulation filter.

The breather filter makes an air in and out of the DE to prevent unnecessary pressure around the

spindle when the disk starts or stops rotating. When disk drives are transported under conditions

where the air pressure changes a lot, filtered air is circulated in the DE.

The circulation filter cleans out dust and dirt from inside the DE. The disk drive cycles air

continuously through the circulation filter through an enclosed loop air cycle system operated by a

blower on the rotating disk.

Содержание MPA3017AT

Страница 1: ...C141 E034 02EN MPA3017AT MPA3026AT MPA3035AT MPA3043AT MPA3052AT DISK DRIVES PRODUCT MANUAL ...

Страница 29: ...C141 E034 02EN 3 2 Figure 3 1 Dimensions ...

Страница 44: ...C141 E034 02EN 4 5 Figure 4 2 MPA30xxAT Block diagram ...

Страница 50: ...C141 E034 02EN 4 11 Figure 4 4 Read write circuit block diagram ...

Страница 52: ...C141 E034 02EN 4 13 Figure 4 6 PR4 signal transfer ...