2.23

Real-Time Clock (RTC)

Zynq Ult devices include an internal real-time clock. The internal RTC can be accessed by the plat-

form management unit (PMU) - more information on the PMU is available in the Zynq Ult MPSoC

Technical Reference Manual [19].

The RTC crystal pad input and crystal pad output are connected on the XU1 SoC module to a

32.768 kHz oscillator.

Starting with revision 2 modules, a 1.2 V LDO is used to generate the battery voltage for the built-in RTC

(supplied to VCC_PSBATT pin), based on the VCC_BAT voltage mapped to the module connector. This pin

can be connected directly to a 3 V battery on the base board. Please refer to the Enclustra Module Pin

Connection Guidelines [11] for details.

On revision 1 modules, the battery voltage is generated using a voltage divider.

An external RTC (separate chip, not within the MPSoC) may be assembled optionally on the XU1

SoC module.

2.24

Secure EEPROM

The secure EEPROM is used to store the module type and serial number, as well as the Ethernet MAC address

and other information. It is connected to the I2C bus.

The secure EEPROM must not be used to store user data.

Please refer to Section 4.4 for details on the content of the EEPROM.

2.24.1

EEPROM Type

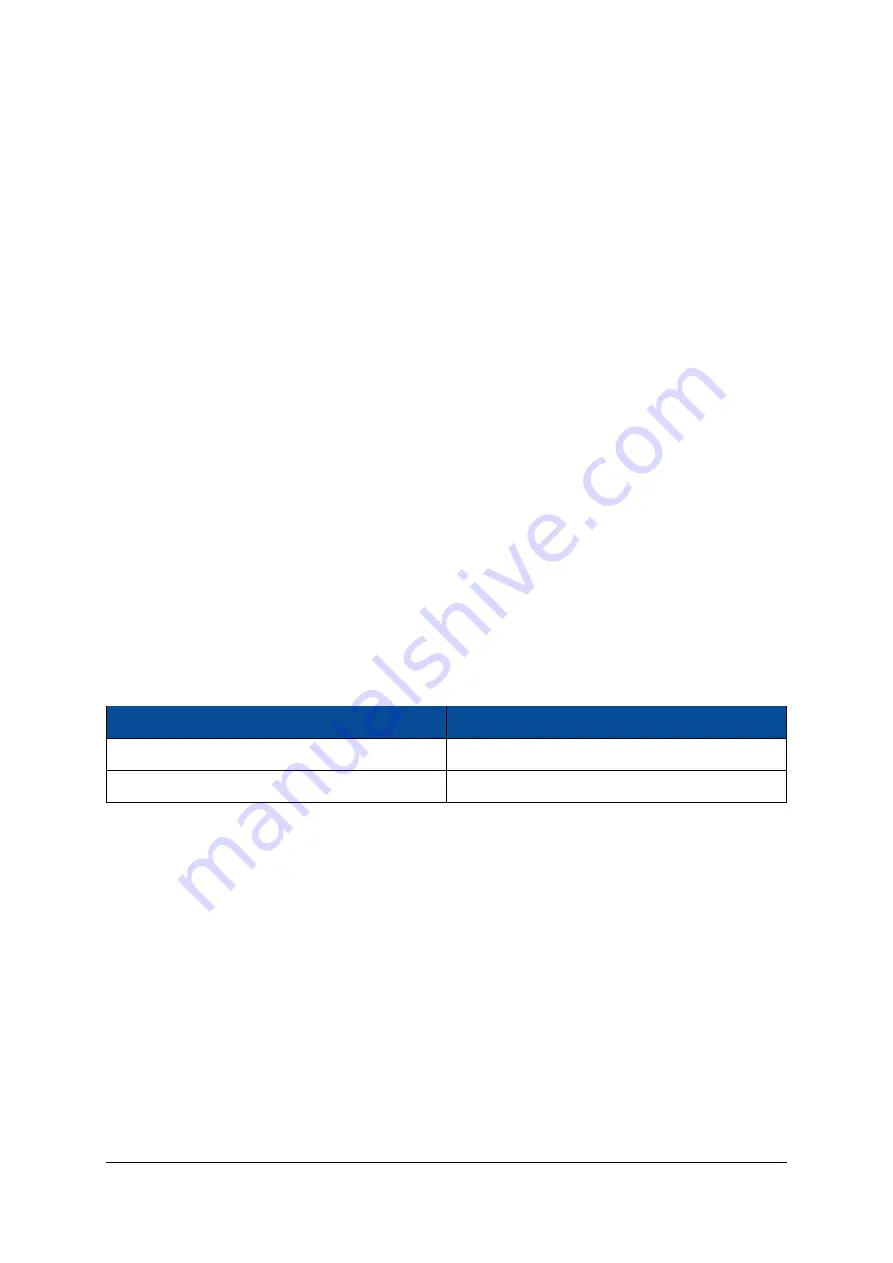

Table 34 describes the equipped EEPROM device type on the XU1 SoC module.

Type

Manufacturer

ATSHA204A-MAHDA-T (default)

Atmel

DS28CN01 (assembly option)

Maxim

Table 34: EEPROM Type

An example demonstrating how to read data from the EEPROM is included in the XU1 SoC module

reference design [2].

2.25

Debug Connector

The XU1 SoC module may optionally be equipped with a debug connector that allows the user to

perform debug operations using JTAG or TRACE signals connected to the ARM DAP, to monitor and control

FPGA configuration signals and to have access to the I2C bus and UART.

Note that starting with revision 3, the debug connector is not offered as an optional feature anymore. The

related circuitry has been completely removed, including the MIO pin mappings for PJTAG, TRACE, and

debug UART interfaces. PJTAG boot mode is also not supported any longer. The signals that were mapped

to the debug connector have been renamed to reflect the changes.

D-0000-428-001

46 / 66

Version 13, 15.08.2019