DS632F1

31

CS44800

4.4.2

Auto Rate Detect

The CS44800 will automatically determine the incoming sample rate, DAI_LRCK, to master clock,

DAI_MCLK, ratio and configure the appropriate internal clock divider such that the sample rate convertor

receives the required clock rate. A minimum DAI_MCLK rate of 128Fs is required for proper operation.

The supported DAI_MCLK to DAI_LRCK ratios are shown in

Table 1 on page 26

.

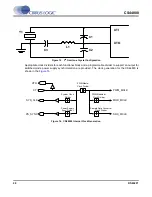

4.4.3

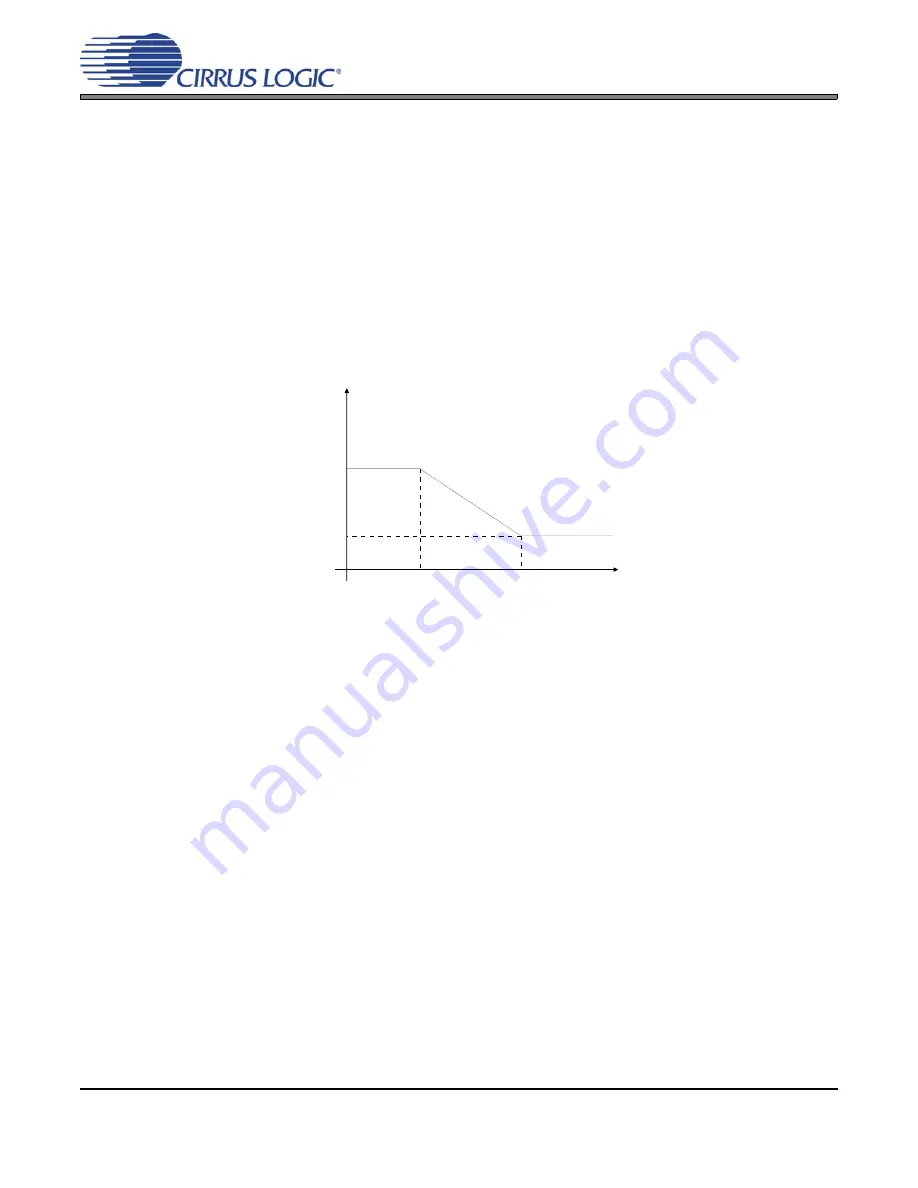

De-Emphasis

The CS44800 includes on-chip digital de-emphasis filters. The de-emphasis feature is included to accom-

modate older audio recordings that utilize pre-emphasis equalization as a means of noise reduction.

shows the de-emphasis curve. The frequency response of the de-emphasis curve will scale pro-

portionally with changes in sample rate, Fs. The required de-emphasis filter for 32 kHz, 44.1 kHz, or

48 kHz is selected via the de-emphasis control bits in

“Misc. Configuration (address 04h)” on page 52

.

Gain

dB

-10dB

0dB

Frequency

T2 = 15 µs

T1=50 µs

F1

F2

3.183 kHz

10.61 kHz

Figure 23. De-Emphasis Curve