20

DS632F1

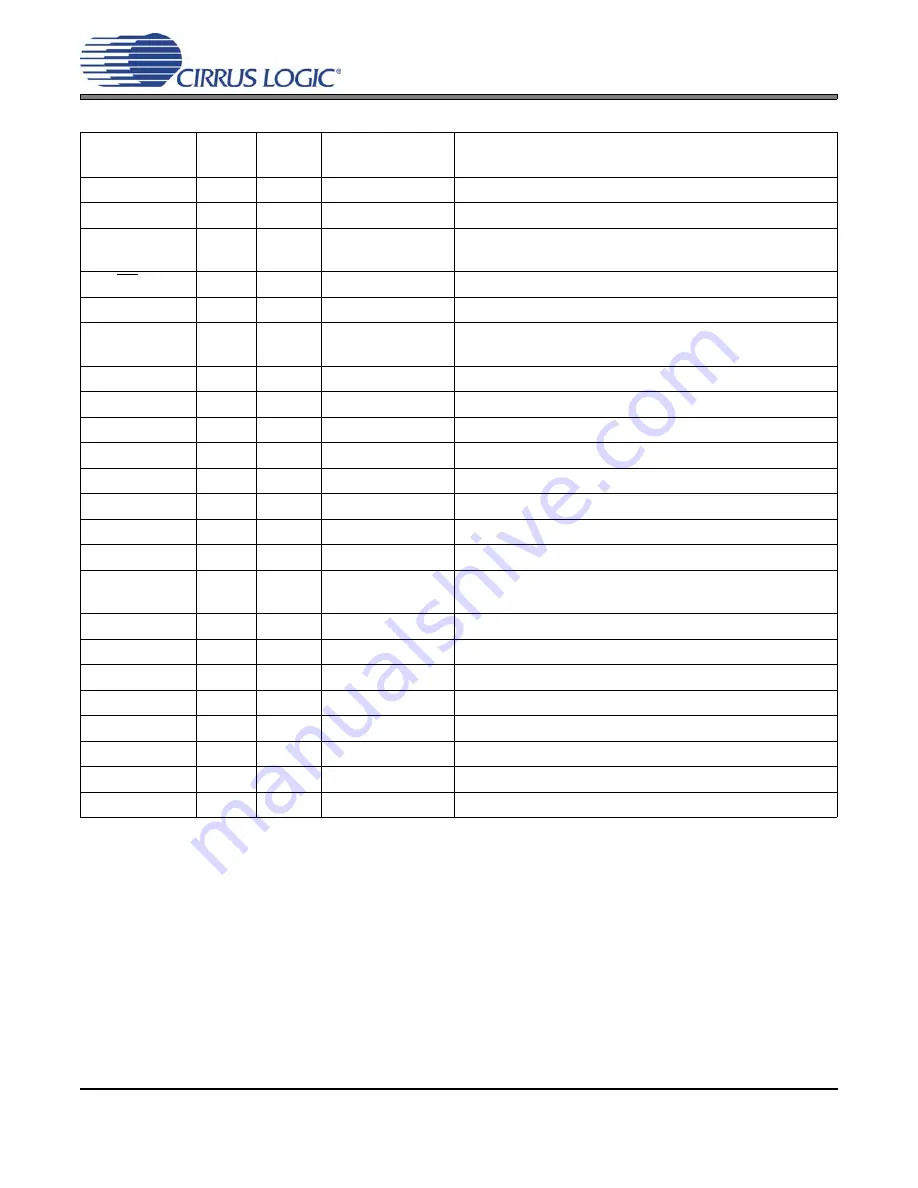

CS44800

2.1

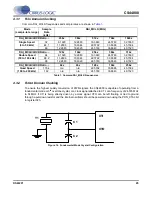

I/O Pin Characteristics

Signal Name

Power

Rail

I/O

Driver

Receiver

RST

VLC

Input

-

2.5 V and 3.3/5.0 V TTL Compatible.

SCL/CCLK

VLC

Input

-

2.5 V and 3.3/5.0 V TTL Compatible, with Hysteresis.

SDA/CDOUT

VLC

Input /

Output

2.5-5.0 V,

CMOS/Open Drain

2.5 V and 3.3/5.0 V TTL Compatible, with Hysteresis.

AD0/CS

VLC

Input

-

2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-up.

AD1/CDIN

VLC

Input

-

2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-up.

INT

VLC

Output

2.5-5.0 V,

CMOS/Open Drain

-

MUTE

VLC

Input

-

2.5 V and 3.3/5.0 V TTL Compatible.

DAI_SDINx

VLS

Input

-

2.5 V and 3.3/5.0 V TTL Compatible.

DAI_SCLK

VLS

Input

-

2.5 V and 3.3/5.0 V TTL Compatible.

DAI_LRCK

VLS

Input

-

2.5 V and 3.3/5.0 V TTL Compatible.

DAI_MCLK

VLS

Input

-

2.5 V and 3.3/5.0 V TTL Compatible.

SYS_CLK

VLS

Output

2.5-5.0 V, CMOS

-

XTI

VDX

Input

-

2.5 V and 3.3/5.0 V TTL Compatible, Internal pull-down.

XTO

VDX

Output

-

-

GPIOx

VDP

Input /

Output

3.3/5.0 V,

CMOS/Open Drain

3.3/5.0 V TTL Compatible.

P/-

VDP

Output

3.3/5.0 V, CMOS

-

P/-

VDP

Output

3.3/5.0 V, CMOS

-

PSR_MCLK

VDP

Output

3.3/5.0 V, CMOS

-

PSR_SYNC

VDP

Input

-

3.3/5.0 V TTL Compatible, Internal pull-up.

PSR_DATA

VDP

Input

-

3.3/5.0 V TTL Compatible, Internal pull-up.

PSR_EN

VDP

Output

3.3/5.0 V, CMOS

-

PSR_RESET

VDP

Output

3.3/5.0 V, CMOS

-

PS_SYNC

VDP

Output

3.3/5.0 V, CMOS

-