28

DS632F1

CS44800

4.4.1.1

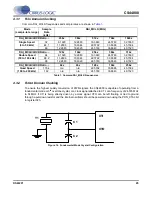

I²S Data Format

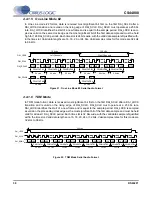

For I²S, data is received most significant bit first, one DAI_SCLK delay after the transition of DAI_LRCK,

and is valid on the rising edge of DAI_SCLK. For the I²S format, the left channel data is presented when

DAI_LRCK is low; the right channel data is presented when DAI_LRCK is high.

4.4.1.2

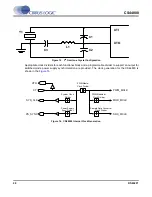

Left-Justified Data Format

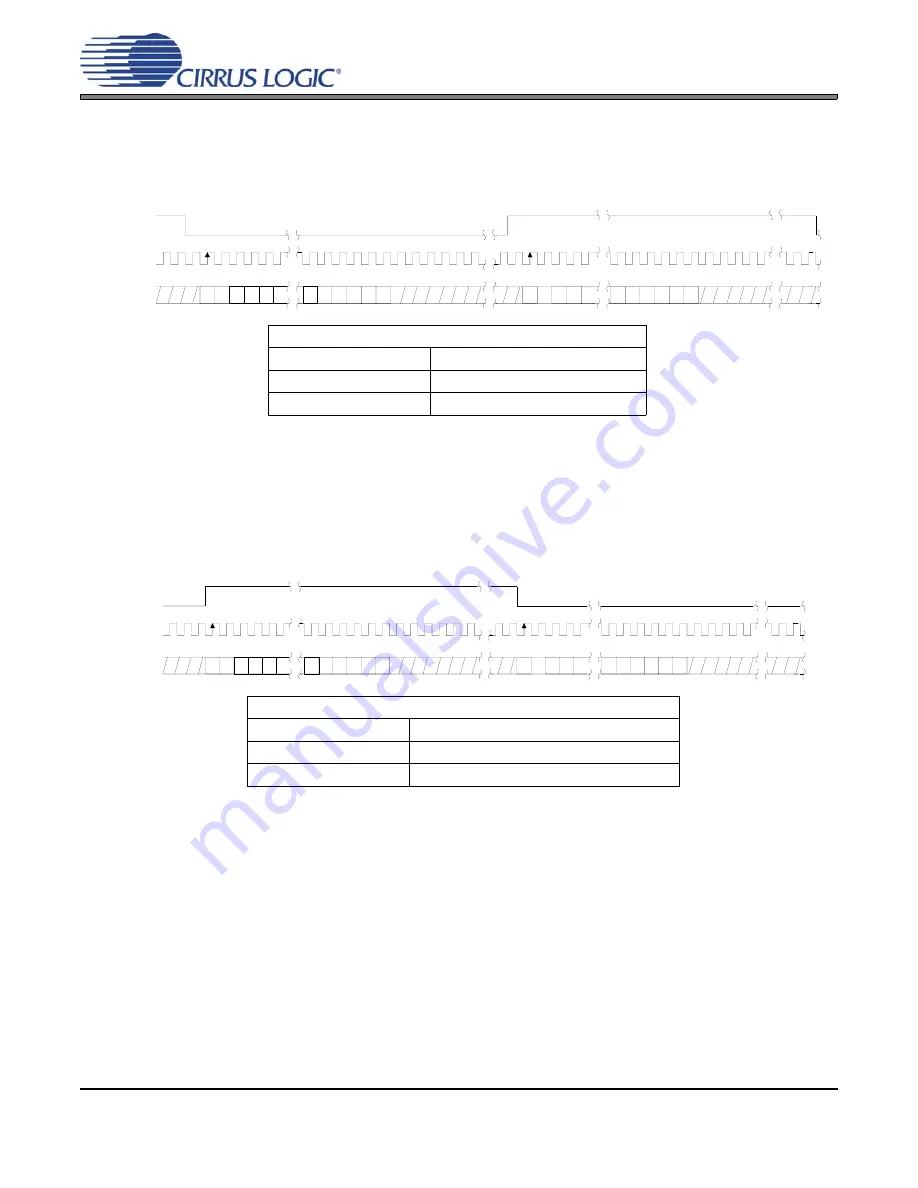

For left-justified format, data is received most significant bit first on the first DAI_SCLK after a DAI_LRCK

transition and is valid on the rising edge of DAI_SCLK. For the left-justified format, the left channel data

is presented when DAI_LRCK is high and the right channel data is presented when DAI_LRCK is low.

Left C ha nnel

R ig ht C ha n nel

DAI_SDINx

+3 +2 +1

+5 +4

-1 -2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 -3 -4

M SB

M SB

LSB

LSB

DAI_LRCK

DAI_SCLK

Figure 17. I²S Serial Audio Formats

I²S Mode, Data Valid on Rising Edge of DAI_SCLK

Bits/Sample

SCLK Rates

16

32, 48, 64, 128, 256 Fs

18 to 24

48, 64, 128, 256 Fs

DAI_LRCK

DAI_SCLK

Left Channel

Right Channel

DAI_SDINx

+3 +2 +1

+5 +4

-1 -2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 -3 -4

MSB

LSB

MSB

LSB

Figure 18. Left-Justified Serial Audio Formats

Left-Justified Mode, Data Valid on Rising Edge of DAI_SCLK

Bits/Sample

SCLK Rate(s)

16

32, 48, 64, 128, 256 Fs

18 to 24

48, 64, 128, 256 Fs