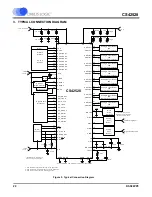

CS42528

22

DS586PP5

4.2.2

High Pass Filter and DC Offset Calibration

The high pass filter continuously subtracts a measure of the DC offset from the output of the decimation

filter. The high pass filter can be independently enabled and disabled. If the HPF_Freeze bit is set during

normal operation, the current value of the DC offset for the corresponding channel is frozen and this DC

offset will continue to be subtracted from the conversion result. This feature makes it possible to perform

a system DC offset calibration by:

1) Running the CS42528 with the high pass filter enabled until the filter settles. See the Digital Filter

Characteristics for filter settling time.

2) Disabling the high pass filter and freezing the stored DC offset.

The high pass filters are controlled using the HPF_FREEZE bit in the register “Misc Control (address 05h)”

on page 52.

4.3

Analog Outputs

4.3.1

Line Level Outputs and Filtering

The CS42528 contains on-chip buffer amplifiers capable of producing line level differential outputs. These

amplifiers are biased to a quiescent DC level of approximately VQ.

The delta-sigma conversion process produces high frequency noise beyond the audio passband, most of

which is removed by the on-chip analog filters. The remaining out-of-band noise can be attenuated using

an off-chip low pass filter. See “DAC Output Filter” on page 76 for a recommended output buffer. This filter

configuration accounts for the normally differing AC loads on the AOUT+ and AOUT- differential output

pins. It also shows an AC coupling configuration which minimizes the number of required AC coupling ca-

pacitors. Figure 7 shows the full-scale analog output levels.

4.3.2

Interpolation Filter

To accommodate the increasingly complex requirements of digital audio systems, the CS42528 incorpo-

rates selectable interpolation filters for each mode of operation. A “fast” and a “slow” roll-off filter is avail-

able in Single, Double, and Quad Speed modes. These filters have been designed to accommodate a

variety of musical tastes and styles. The FILT_SEL bit found in the register “Misc Control (address 05h)”

on page 52 selects which filter is used. Filter response plots can be found in Figures 45 to

68.

AOUT+

AOUT-

Full-Scale Output Level= (AIN+) - (AIN-)= 5 Vpp

3.95 V

2.7 V

1.45 V

3.95 V

2.7 V

1.45 V

Figure 7. Full-Scale Output