DS586PP5

21

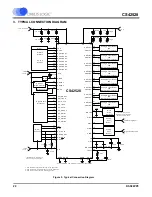

CS42528

4. APPLICATIONS

4.1

Overview

The CS42528 is a highly integrated mixed signal 24-bit audio codec comprised of 2 analog-to-digital con-

verters (ADC), implemented using multi-bit delta-sigma techniques, 8 digital-to-analog converters (DAC)

and a 192 kHz digital audio S/PDIF receiver. Other functions integrated within the codec include indepen-

dent digital volume controls for each DAC, digital de-emphasis filters for DAC and S/PDIF, digital gain

control for ADC channels, ADC high-pass filters, an on-chip voltage reference, and an 8:2 mux for S/PDIF

sources. All serial data is transmitted through two configurable serial audio interfaces with standard serial

interface support as well as enhanced one line modes of operation allowing up to 6 channels of serial au-

dio data on one data line. All functions are configured through a serial control port operable in SPI mode

or in I

2

C mode. Figure 5 show the recommended connections for the CS42528.

The CS42528 operates in one of three oversampling modes based on the input sample rate. Mode selec-

tion is determined by the FM bits in register “Functional Mode (address 03h)” on page 49. Single-Speed

mode (SSM) supports input sample rates up to 50 kHz and uses a 128x oversampling ratio. Double-

Speed mode (DSM) supports input sample rates up to 100 kHz and uses an oversampling ratio of 64x.

Quad-Speed mode (QSM) supports input sample rates up to 192 kHz and uses an oversampling ratio of

32x.

Using the receiver clock recovery PLL, a low jitter clock is recovered from the incoming S/PDIF data

stream. The recovered clock or an externally supplied clock attached to the OMCK pin can be used as

the System Clock.

4.2

Analog Inputs

4.2.1

Line Level Inputs

AINR+, AINR-, AINL+, and AINL- are the line level differential analog inputs. The analog signal must be

externally biased to VQ, approximately 2.7 V, before being applied to these inputs. The level of the signal

can be adjusted for the left and right ADC independently through the ADC Left and Right Channel Gain

Control Registers on page 62. The ADC output data is in 2’s complement binary format. For inputs above

positive full scale or below negative full scale, the ADC will output 7FFFFFH or 800000H, respectively and

cause the ADC Overflow bit in the register “Interrupt Status (address 20h) (Read Only)” on page 64 to be

set to a ‘1’. The RXP/GPO pins may also be configured to indicate an overflow condition has occurred in

the ADC. See “RXP/General Purpose Pin Control (addresses 29h to 2Fh)” on page 70 for proper config-

uration. Figure 6 shows the full-scale analog input levels. See “ADC Input Filter” on page 76 for a recom-

mended input buffer.

AIN+

AIN-

Full-Scale Input Level= (AIN+) - (AIN-)= 5.6 Vpp

4.1 V

2.7 V

1.3 V

4.1 V

2.7 V

1.3 V

Figure 6. Full-Scale Analog Input