II - 2

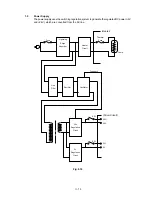

1.2

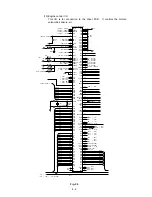

Main PCB Block Diagram

Fig. 2.2 shows a block diagram of the main PCB.

RESET CIRCUIT

P FONT ROM

512 KByte

RAM

(0.5M or 1M Byte)

OPTION RAM

(0.5M or 1M Byte)

OPTION SERIAL I/O

(RS232C & RS422A)

EEPROM (128 8 bit)

CPU

(MC68EC000)

A S I C

OSCILLATOR (15.3MHz)

ADDRESS DECODER

DRAM CONTROL

TIMER

FIFO

CDCC PARALLEL I/O

SOFT SUPPORT

EEPROM I/O

ENGINE CONTROL I/O

TO DRIVER PCB

BUS

INT

Fig. 2.2 Main PCB Block Diagram