60

IC Diagrams

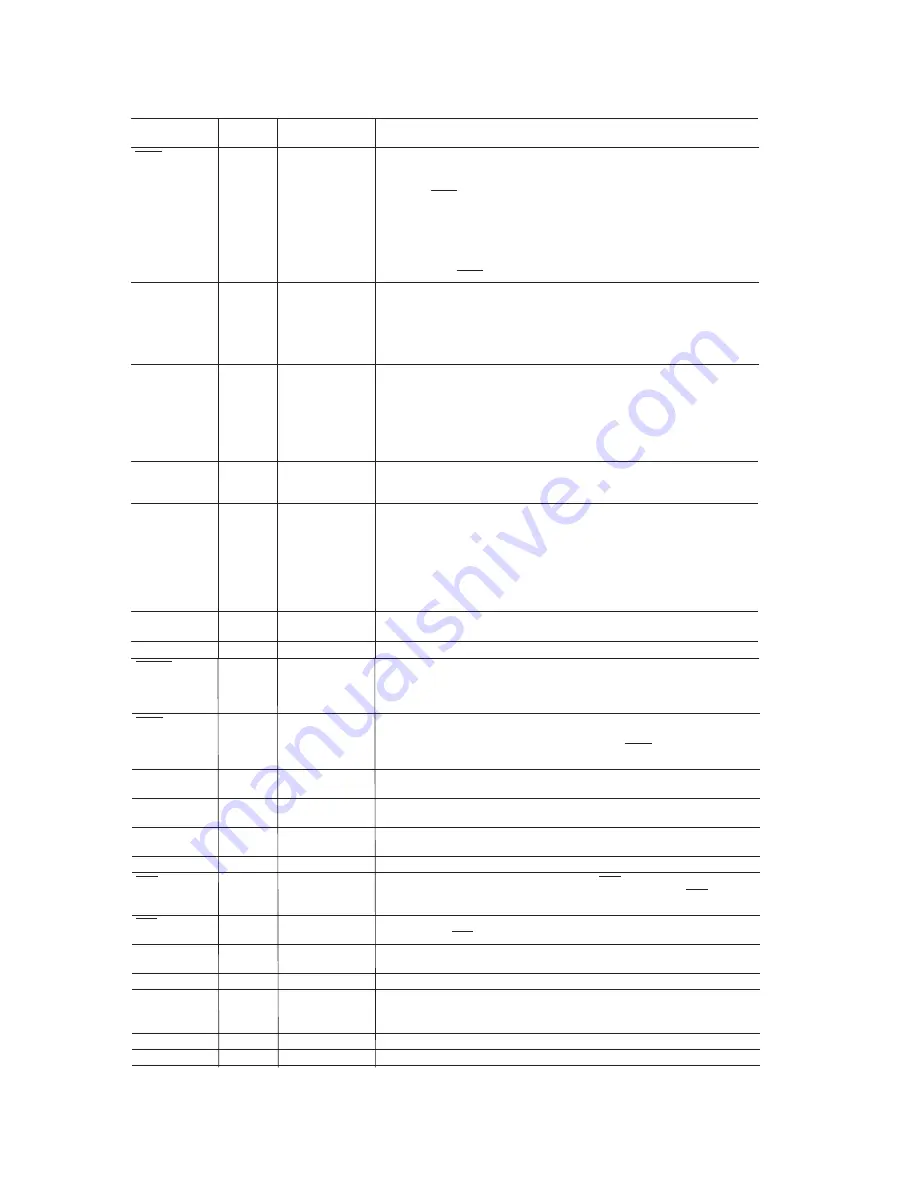

ADSP-21366KBCZ136-BALL, DSP BGA, sheet 2 of 2

SPIDS

I

Input only

Serial Peripheral Interface Slave Device Select

. An active low signal used to select

the processor as an SPI slave device. This input signal behaves like a chip select, and

is provided by the master device for the slave devices. In multimaster mode the

processor’s SPIDS signal can be driven by a slave device to signal to the processor (as

SPI master) that an error has occurred, as some other device is also trying to be the

master device. If asserted low when the device is in master mode, it is considered a

multimaster error. For a single-master, multiple-slave configuration where flag pins

are used, this pin must be tied or pulled high to V

DDEXT

on the master device. For

processor to processor SPI interaction, any of the master processor’s flag pins can be

used to drive the SPIDS signal on the SPI slave device.

MOSI

I/O (O/D)

(pu)

Three-state with

pull-up enabled

SPI Master Out Slave In

. If the ADSP-2136x is configured as a master, the MOSI pin

becomes a data transmit (output) pin, transmitting output data. If the processor is

configured as a slave, the MOSI pin becomes a data receive (input) pin, receiving input

data. In a SPI interconnection, the data is shifted out from the MOSI output pin of the

master and shifted into the MOSI input(s) of the slave(s). MOSI has a 22.5 k

Ω

internal

pull-up resistor.

MISO

I/O (O/D)

(pu)

Three-state with

pull-up enabled

SPI Master In Slave Out

. If the ADSP-2136x is configured as a master, the MISO pin

becomes a data receive (input) pin, receiving input data. If the processor is configured

as a slave, the MISO pin becomes a data transmit (output) pin, transmitting output

data. In an SPI interconnection, the data is shifted out from the MISO output pin of the

slave and shifted into the MISO input pin of the master. MISO has a 22.5 k

Ω

internal

pull-up resistor. MISO can be configured as O/D by setting the OPD bit in the SPICTL

register.

BOOTCFG1–0

I

Input only

Boot Configuration Select

. This pin is used to select the boot mode for the processor.

The BOOTCFG pins must be valid before reset is asserted.

CLKIN

I

Input only

Local Clock In

. Used in conjunction with XTAL. CLKIN is the ADSP-2136x clock input.

It configures the ADSP-2136x to use either its internal clock generator or an external

clock source. Connecting the necessary components to CLKIN and XTAL enables the

internal clock generator. Connecting the external clock to CLKIN while leaving XTAL

unconnected configures the processors to use the external clock source such as an

external clock oscillator. The core is clocked either by the PLL output or this clock input

depending on the CLKCFG1–0 pin settings. CLKIN may not be halted, changed, or

operated below the specified frequency.

XTAL

O

Output only

2

Crystal Oscillator Terminal

. Used in conjunction with CLKIN to drive an external

crystal.

CLKCFG1–0

I

Input only

Core/CLKIN Ratio Control

. These pins set the start up clock frequency.

Pin Descriptions (Continued)

Pin Type

State During and

After Reset

Description

RSTOUT/CLKOUT O

Output only

Local Clock Out/Reset Out

. Drives out the core reset signal to an external device.

CLKOUT can also be configured as a reset out pin. The functionality can be switched

between the PLL output clock and reset out by setting Bit 12 of the PMCTREG register.

The default is reset out.

RESET

I/A

Input only

Processor Reset

. Resets the ADSP-2136x to a known state. Upon deassertion, there is

a 4096 CLKIN cycle latency for the PLL to lock. After this time, the core begins program

execution from the hardware reset vector address. The RESET input must be asserted

(low) at power-up.

TCK

I

Input only

3

Test Clock (JTAG)

. Provides a clock for JTAG boundary scan. TCK must be asserted

(pulsed low) after power-up or held low for proper operation of the processors.

TMS

I/S

(pu)

Three-state with

pull-up enabled

Test Mode Select (JTAG)

. Used to control the test state machine. TMS has a 22.5 k

Ω

internal pull-up resistor.

TDI

I/S

(pu)

Three-state with

pull-up enabled

Test Data Input (JTAG)

. Provides serial data for the boundary scan logic. TDI has a

22.5 k

Ω

internal pull-up resistor.

TDO

O

Three-state

4

Test Data Output (JTAG)

. Serial scan output of the boundary scan path.

TRST

I/A

(pu)

Three-state with

pull-up enabled

Test Reset (JTAG)

. Resets the test state machine. TRST must be asserted (pulsed low)

after power-up or held low for proper operation of the ADSP-2136x. TRST has a

22.5 k

Ω

internal pull-up resistor.

EMU

O (O/D)

(pu)

Three-state with

pull-up enabled

Emulation Status

. Must be connected to the processor’s JTAG emulators target board

connector only. EMU has a 22.5 k

Ω

internal pull-up resistor.

V

DDINT

P

Core Power Supply

. Nom1.2 V dc for the K, B grade models, and

1.0 V dc for the Y and W grade models, and supplies the processor’s core (13 pins).

V

DDEXT

P

I/O Power Supply

. Nom3.3 V dc (6 pins).

A

VDD

P

Analog Power Supply

. Nom1.2 V dc for the K, B grade models, and

1.0 V dc for the Y and W Grade models, and supplies the processor’s internal PLL (clock

generator).

A

VSS

G

Analog Power Supply Return

.

GND

G

Power Supply Return

.

(54 pins)

Содержание T1 ToneMatch

Страница 10: ...10 Figure 2 T1 ToneMatch Audio Engine Exploded View ...

Страница 52: ...52 Figure 3 DSP PCB Top Component Layout and Etch Circuit Board Layout Diagrams ...

Страница 53: ...53 Figure 4 DSP PCB Top Component Layout and Power Layer Etch Circuit Board Layout Diagrams ...

Страница 54: ...54 Figure 5 DSP PCB Top Component Layout and Ground Layer Etch Circuit Board Layout Diagrams ...

Страница 55: ...55 Figure 6 DSP PCB Bottom Component Layout and Etch Circuit Board Layout Diagrams ...