ZedBoard Booting and Configuration Guide

ISE Design Suite 14.1

14

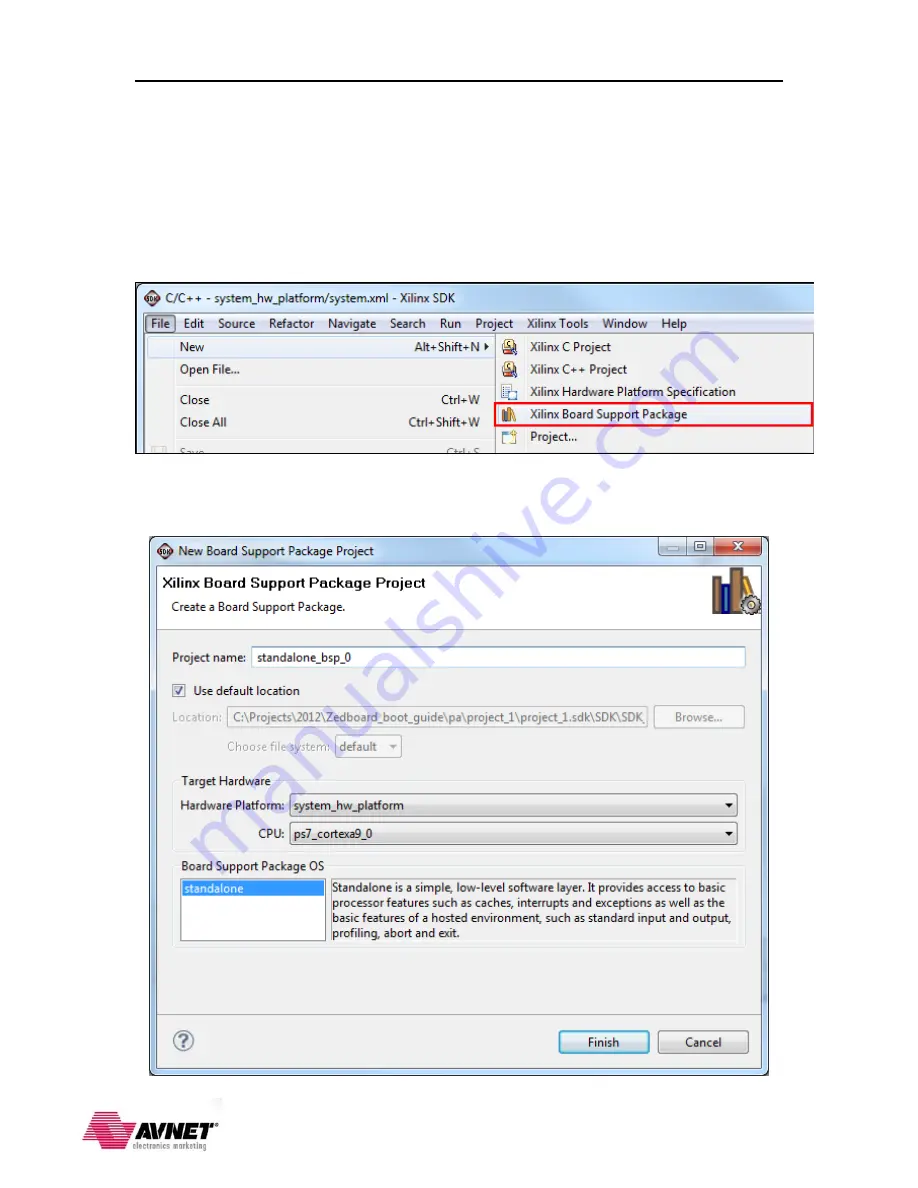

Create the Board Support Package

The first thing we need to create in our empty workspace is a Board Support Package

(BSP) on which individual projects can be built. Multiple BSPs and multiple application

projects can be held in a single SDK workspace. To begin, create a basic BSP that is

adequate for the GPIO test and FSBL applications we intend to run.

1.

From the SDK main menu, select

File

New

Xilinx Board Support Package

.

2.

Accept the defaults for the

Project name, Hardware Platform, CPU, and OS

.

Click

Finish

to continue.