AT90S8414

Preliminary

4-39

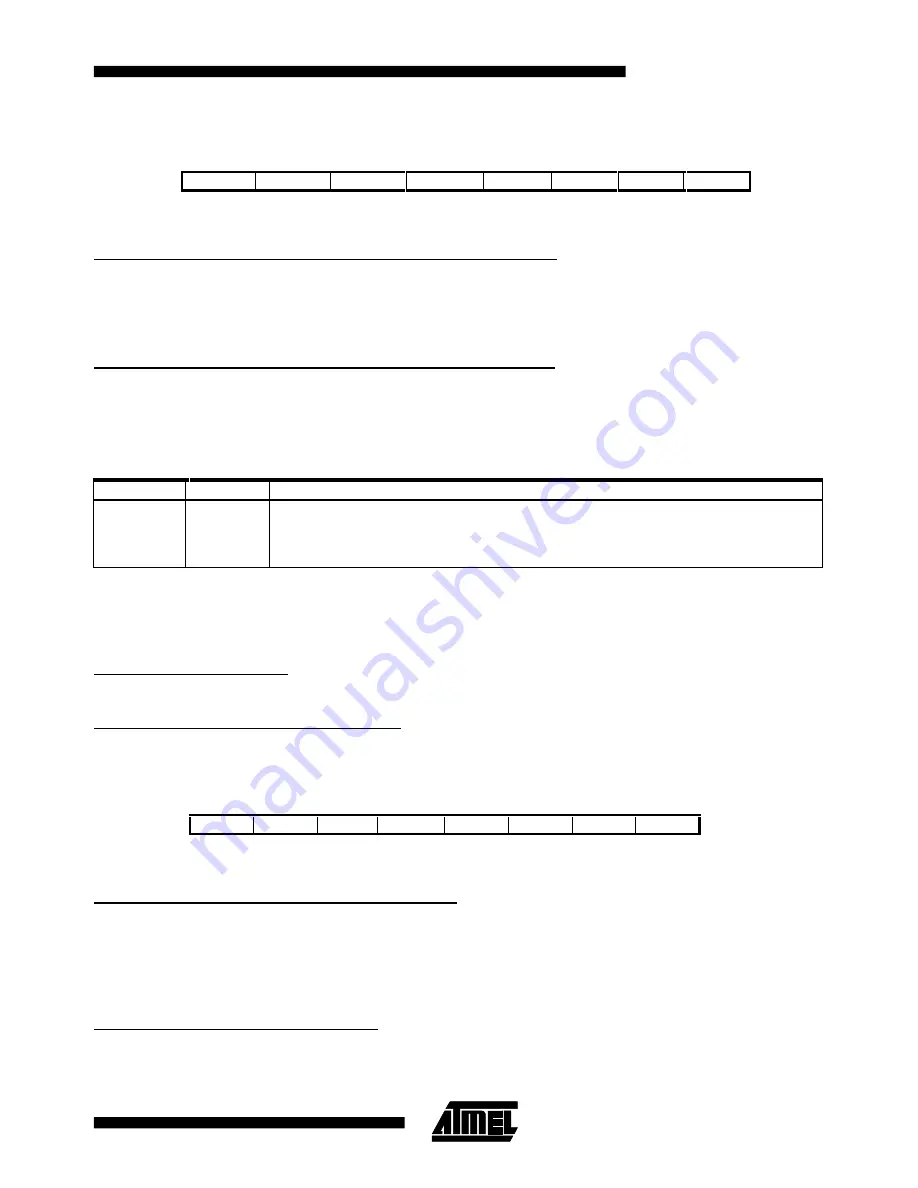

THE TIMER/COUNTER1 CONTROL REGISTER A - TCCR1A

Bit

7

6

5

4

3

2

1

0

$2F

COM1A1

COM1A0

COM1B1

COM1B0

-

-

-

PWM1

TCCR1A

Read/Write

R/W

R/W

R/W

R/W

R

R

R

R/W

Initial value

0

0

0

0

0

0

0

0

Bits 7,6 - COM1A1, COM1A0 : Compare Output Mode1A, bits 1 and 0:

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in Timer/Counter1.

Any output pin actions affect pin OC1A - Output CompareA pin 1. Since this is an alternative function to an I/O port, the

corresponding direction control bit must be set (one) to control an output pin. The control configuration is shown in

Table 8.

Bits 5,4 - COM1B1, COM1B0 : Compare Output Mode1B, bits 1 and 0:

The COM1B1 and COM1B0 control bits determine any output pin action following a compare match in Timer/Counter1.

Any output pin actions affect pin OC1B - Output CompareB. Since this is an alternative function to an I/O port, the

corresponding direction control bit must be set (one) to control an output pin. The following control configuration is

given:

Table 8: Compare 1 Mode Select

COM1X1

COM1X0

Description

0

0

Timer/Counter1 disconnected from output pin OC1X

0

1

Toggle the OC1X output line.

1

0

Clear the OC1X output line (to zero).

1

1

Set the OC1X output line (to one).

Notes: X = A or B

In PWM mode, these bits have a different function. Refer to Table 10 for a detailed description.

When changing the COM1X1/COM1X0 bits, Output Compare Interrupts 1 must be disabled by clearing their

Interrupt Enable bits in the TIMSK Register. Otherwise an interrupt can occur when the bits are changed.

Bits 3..1 - Res : Reserved bits:

These bits are reserved bits in the AT90S8414 and always read zero.

Bit 0 - PWM1 : Pulse Width Modulator enable:

This bit enables the PWM mode for Timer/Counter1. This mode is described on Page 4-42.

THE TIMER/COUNTER1 CONTROL REGISTER B - TCCR1B

Bit

7

6

5

4

3

2

1

0

$2E

ICNC1

ICES1

-

-

CTC1

CS12

CS11

CS10

TCCR1B

Read/Write

R/W

R/W

R

R

R/w

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0

Bit 7 - ICNC1 : Input Capture1 Noise Canceler (4 CKs):

When the ICNC1 bit is cleared (zero), the input capture trigger noise canceler function is disabled. The input capture is

triggered at the first rising/falling edge sampled on the ICP - input capture pin - as specified. When the ICNC1 bit is set

(one), four successive samples are measures on the ICP - input capture pin, and all samples must be high/low according

to the input capture trigger specification in the ICES1 bit. The actual sampling frequency is the same as the clock source

frequency selected for the Timer/Counter1.

Bit 6 - ICES1 : Input Capture1 Edge Select:

Содержание AT90S8414

Страница 4: ...4 4 AT90S8414 Preliminary...

Страница 6: ...4 6 AT90S8414 Preliminary Block Diagram Figure 1 The AT90S8414 Block Diagram...

Страница 65: ...AT90S8414 Preliminary 4 65 Figure 50 PORTB Schematic Diagram Pin PB5 Figure 51 PORTB Schematic Diagram Pin PB6...

Страница 68: ...4 68 AT90S8414 Preliminary Figure 53 PORTC Schematic Diagram Pins PC0 PC7...

Страница 87: ...AT90S8414 Preliminary 4 87...