Related Information

Clock Feedback Modes

on page 2-14

PLL Control Signals Parameter Settings

The parameter settings for the control signals are located on the Inputs/Lock page of the ALTPLL IP core

parameter editor.

Turn on the control signal you want to create from the options available.

Related Information

PLL Control Signals

on page 2-13

Programmable Bandwidth Parameter Settings

You can configure the bandwidth of the ALTPLL IP core on the Bandwidth/SS page of the ALTPLL IP

core parameter editor.

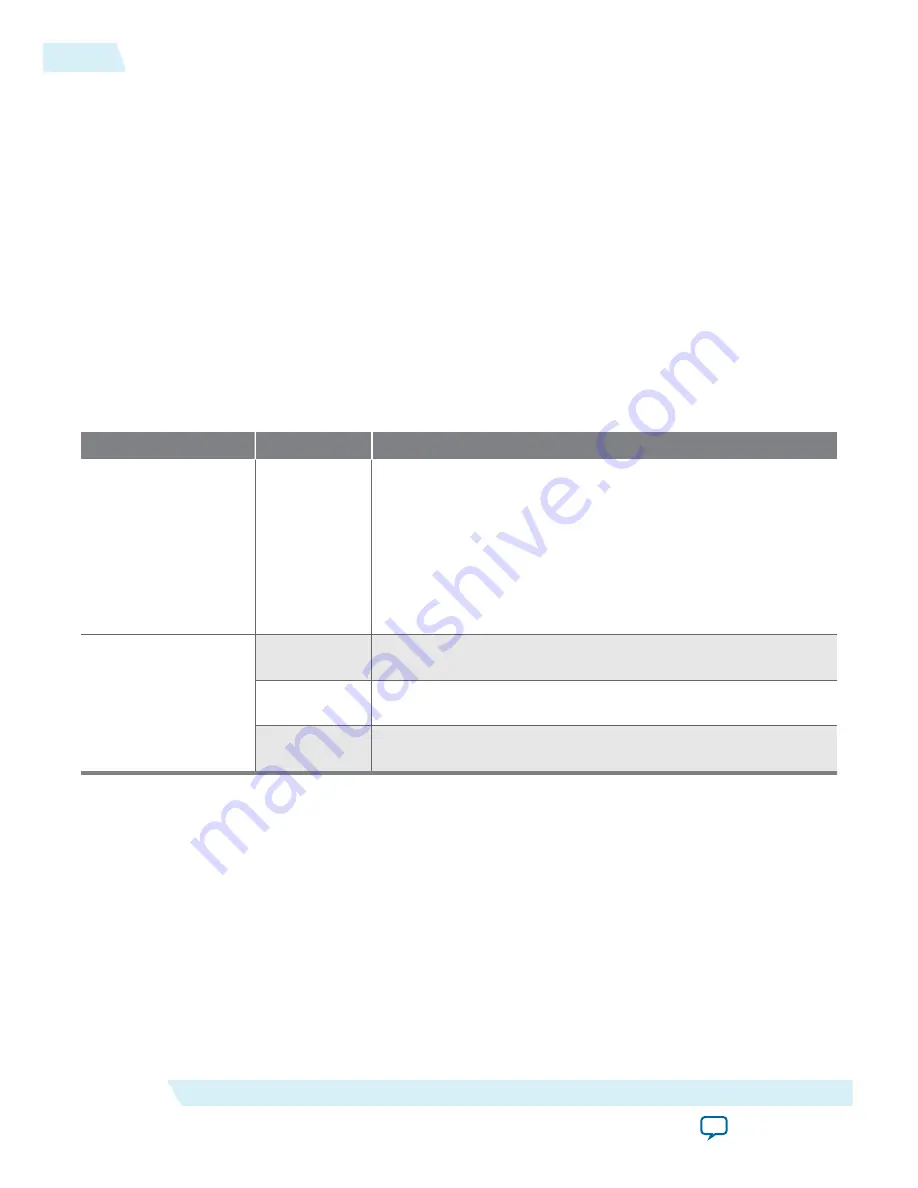

Table 6-2: Bandwidth Configuration Parameter Editor Settings

Parameter

Value

Description

Auto

—

The ALTPLL parameter editor chooses the best possible

bandwidth values to achieve the desired PLL settings. In some

cases, you can get a bandwidth value outside the Low and High

preset range.

You can use the programmable bandwidth feature with the clock

switchover feature to get the PLL output settings that you desire.

You must set the bandwidth to Auto if you want to enable the

spread-spectrum feature.

Preset

Low

PLL with a low bandwidth has better jitter rejection but a slower

lock time.

Medium

PLL with a medium bandwidth has a balance between lock time

and jitter rejection.

High

PLL with a high bandwidth has a faster lock time but tracks more

jitter.

The table on the right in the Bandwidth/SS page shows the values of the following components:

• Charge pump current

• Loop filter resistance

• Loop filter capacitance

•

M

counter

These parameter settings create no additional top-level ports.

Related Information

•

Programmable Bandwidth

on page 2-19

•

Programmable Bandwidth with Advanced Parameters

on page 4-10

•

Charge Pump and Loop Filter

on page 4-13

6-2

PLL Control Signals Parameter Settings

UG-M10CLKPLL

2014.12.15

Altera Corporation

ALTPLL IP Core References

Send Feedback