INDUSTRIAL I/O PACK SERIES AVME9675 VME64x 6U CARRIER BOARD

___________________________________________________________________________________________

- 7 -

Note: The letter in front of the number indentifies the IP Module

Slot. The number indentifies the I/O pin number of that IP

Module.

Example: A46

A = IP Module in Slot “A”

46 = I/O Pin number “46”

(This pin on the IP Module connects to P2, Pin 28, Row C.)

Shaded area are pins defined under the VME64x bus specification.

BOLD ITALIC Logic Lines are NOT USED by the carrier board.

(

φ

) = Elongated (mate first, break last) connector contact.

The I/O signals for the P2 connector are mapped per the IP

Module I/O to VME64x bus Standard (ANSI/VITA 4.1-1996). Refer

to this standard for additional information on the VME64x bus

signals.

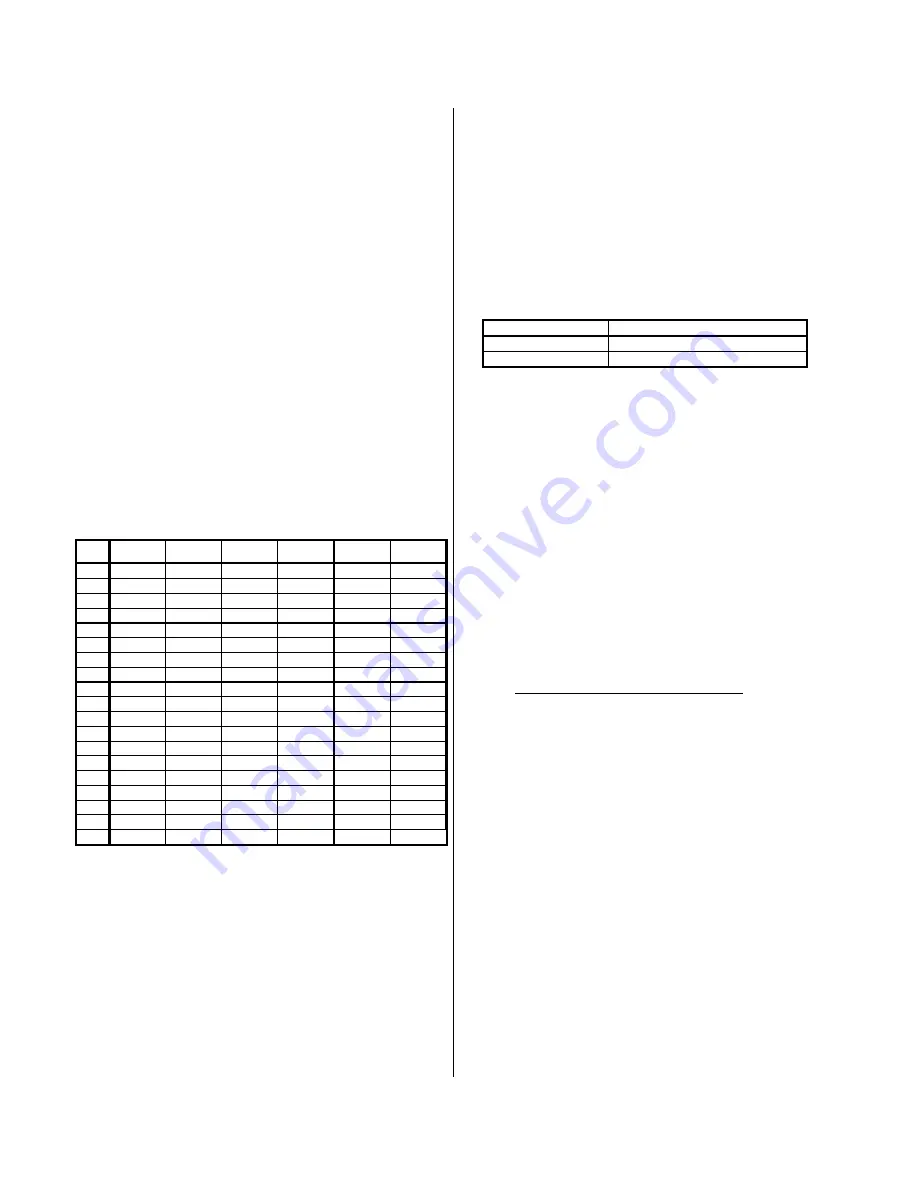

VME64x bus Connections for P0

Table 2.5 lists the pin assignments for the VME64x bus signals

at the P0 connector. The P0 connector is the center connector on

the AVME9675 board, as viewed from the front. The connector

consists of 6 rows of 19 pins labeled A, B, C, D, E, and F. Pin A1

is located at the upper right hand corner of the connector near the

center of the board, viewed from the front component side.

The I/O signals for the P0 connector are mapped per the IP

Module I/O to VME64Xbus Standard (ANSI/VITA 4.1-1996). Refer

to this standard for additional information on the VME64x bus

signals.

TABLE 2.5: VME64x bus P0 CONNECTIONS

Pin

Row A

Row B

Row C

Row D

Row E

Row F

1

D1

D2

D3

D4

D5

GND

2

D6

D7

D8

D9

D10

NP

3

D11

D12

D13

D14

D15

GND

4

D16

D17

D18

D19

D20

NP

5

D21

D22

D23

D24

D25

GND

6

D26

D27

D28

D29

D30

NP

7

D31

D32

D33

D34

D35

GND

8

D36

D37

D38

D39

D40

NP

9

D41

D42

D43

D44

D45

GND

10

D46

D47

D48

D49

D50

NP

11

C1

C2

C3

C4

C5

GND

12

C6

C7

C8

C9

C10

NP

13

C11

C12

C13

C14

C15

GND

14

C16

C17

C18

C19

C20

NP

15

C21

C22

C23

C24

C25

GND

16

C26

C27

C28

C29

C30

NP

17

C31

C32

C33

C34

C35

GND

18

C36

C37

C38

C39

C40

NP

19

C41

C42

C43

C44

C45

GND

Note: The letter in front of the number indentifies the IP Module

Slot. The number indentifies the I/O pin number of that IP

Module.

Example: D1

D = IP Module in Slot “D”

1 = I/O Pin number “1”

(This pin on the IP Module connects to P0, Pin 1, Row A.)

(NP) = No Pin for PO connector (Row F is for upper ground shield).

•

The P0 connector will not be present on AVME9675-2 models.

POWER-UP TIMING AND LOADING

The AVME9675 board uses a Field Programmable Gate-Array

(FPGA) to handle the bus interface and control logic timing. Upon

power-up, the FPGA automatically clocks in configuration vectors

from a local PROM to initialize the logic circuitry for normal

operation. This time is measured as the first 145mS (typical) after

the +5 Volt supply rises to +2.5 Volts at power-up. The VME64x

bus specification requires that the bus master drive the system reset

for the first 200mS after power-up, thus inhibiting any data transfers

from taking place.

IP control registers are also reset following a power-up

sequence, disabling interrupts, etc. (see Section 3 for details).

DATA TRANSFER TIMING

VME64x bus data transfer time is measured from the falling

edge of DSx* to the falling edge of DTACK* during a normal data

transfer cycle. Typical transfer times are given in the following table.

Register

Data Transfer Time

All Carrier Registers

450 nS, Typical.

IP Registers

450 nS, Typical, If No Wait States*

* See IP module specifications for information on wait states. IP

module register access time will increase by the number of wait

states multiplied by 125nS (the period of the 8 MHz clock).

FIELD GROUNDING CONSIDERATIONS

Carrier boards are designed with passive filters on each supply

line to each IP module. This provides maximum filtering and signal

isolation between the IP modules and the carrier board. However,

the boards are considered non-isolated, since there is electrical

continuity between the VME64x bus and the IP grounds. Therefore,

unless isolation is provided on the IP module itself, the field I/O

connections are not isolated from the VME64x bus. Care should be

taken in designing installations without isolation to avoid ground

loops and noise pickup. This is particularly important for analog I/O

applications when a high level of accuracy/resolution is needed (12-

bits or more). Contact your Acromag representative for information

on our many isolated signal conditioning products that could be used

to interface to the IP input/output modules.

3.0 PROGRAMMING INFORMATION

This Section provides the specific information necessary to

operate the AVME9675 non-intelligent carrier board.

The AVME9675 implements Geographical Addressing and the

Configuration ROM / Control and Status Register (CR/CSR) space

as they are defined in the VME64x Standard.

The AVME9675’s CR/CSR Space is 512 KB in size (0x00000

to 0x7FFFF). The AVME9675’s position in the CR/CSR Space

array is determined by the CR/CSR Base Address Register

(CR/CSR BAR). The AVME9675 uses the VME64x Geographical

Addressing method to automatically provide the CR/CSR BAR

value.

GEOGRAPHICAL ADDRESSING

Geographical address capability allows the AVME9675 CR/CSR

space to be addressed upon system initialization and configured

without setting address switches. The CR/CSR Base Address

Register value is derived from the geographical address pins (see

Table 2.3 Row D). The geographical address pins are set by the

system backplane with unique slot addresses and are routed via the

P1 connector to the AVME9675’s FPGA. The FPGA hardware

automatically writes the geographic address into the CR/CSR BAR

upon system power-up. The implementation of geographical

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com