ACCES I/O Products, Inc.

MADE IN THE USA

mPCIe- and M.2-AIO16-16F Family Manual

9

Rev B7a

ADC Counts:

16-

bit two’s complement ADC counts, the ADC conversion result from the samples Channel at the specified Gain, sampled in Differe

ntial or Singled-ended /

Pseudo-Differential mode as indicated by the Diff bit (D19).

Please refer to the “Software Tips” section for details on how to translate RAW

-format ADC data into Volts

—

or skip the hassle and use our AIOAIO.dll API Library:

ADC_GetImmediateV(iBoard, pVolts, iChannel, iRange);, ADC_GetImmediateScanV(iBoard, pVolts[]); etc.

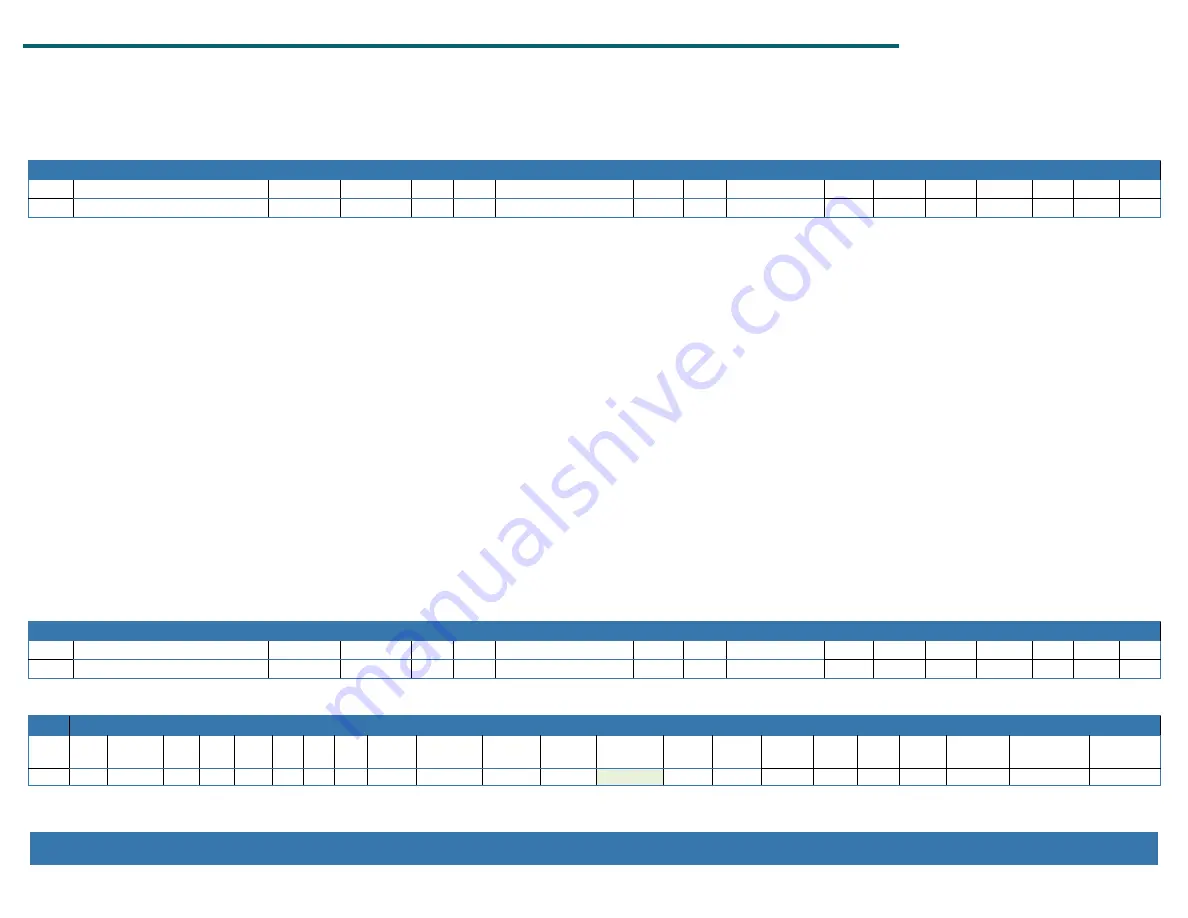

ADC Control, 38 of 32-bit Memory BAR[1]Read/Write 32-bits only

bit D31 through D19

D18

D17

D16 D15 D14 through D12

D11

D10 D9 through D7 D6

D5

D4

D3

D2

D1

D0

Name UNUSED

SCAN

CONFIG

GO

RSV

IN

x

2:0

COM

RSV

Gain2:0

/MUX SEQ1

SEQ0

/TEMP RSV CMS

RSV

Controls ADAS #0, channels 0-7

The ADAS3022 is a very flexible ADC module and we highly recommend you use the AIOAIO.dll-provided API to avoid needing to know the following information.

SCAN: If SCAN is set (to 1)

AND

INx2:0 is non-

zero then each “ADC Start” event will acquire channels 0 through INx2:0 at the rate specified in +14.

CONFIG: If CONFIG is set then the ADC control bits (D15 through D0 of this register) will be written to the ADAS3022

GO:

If GO is set then, if +10 is non-zero the card will begin taking ADC conversions or scans at the rate set via +10; if +10 is zero then a single ADC conversion or scan will be

taken.

INx2:0: INx specifies the individual channel to convert (in non-sequenced modes) or the last channel of the 0-INx sequence to be converted.

COM:

If COM is set then each conversion will be the measurement between the IN+ pin and COMMON (single-ended or pseudo-differential mode). If COM is clear then

differential mode is set, and each conversion will be the measurement between the IN+ and IN- pins.

Gain2:0: If BASIC or non-sequenced mode is configured via the SEQ1:0 bits then Gain2:0 selects the gain to be used for the conversion(s) commanded. If advanced sequence

mode is configured then these bits are ignored (bits 2:0 at +18 take precedence in advanced sequencer mode)

/MUX:

All users should set this bit to “1” unless otherwise instructed by the factory. If MUX is clear (0) then the conversion wil

l be from the auxiliary mux inputs (in non-

sequencer mode) or the sequence will include the aux input (sequencer modes). Not recommended.

SEQ1:0:

Use “00” for non

-

sequenced mode and “10” for advanced sequencer mode. “11” sets basic sequencer mode, and “01” updates the basic sequence

-in-progress. Not

recommended.

/TEMP: If TEMP is clear (0) then the conversion will be from the onboard temperature reference (in non-sequencer mode) or the sequence will include the temperature input

(sequencer modes). Not recommended. Most users should set this bit to 1.

CMS:

Must be set if conversion will occur slower than 1kHz. Must be clear if conversions will occur faster than 900kHz.

ADC Control #2, 3C of 32-bit Memory BAR[1]Read/Write 32-bits only

bit D31 through D19

D18

D17

D16 D15 D14 through D12

D11

D10 D9 through D7 D6

D5

D4

D3

D2

D1

D0

Name UNUSED

RSV

CONFIG

RSV

RSV

IN

x

2:0

COM

RSV

Gain2:0

/MUX SEQ1

SEQ0

/TEMP RSV CMS

RSV

Controls ADAS #1, channels 8-15. Refer to +38, ADC Control #1, for details.

IRQ Enable/Clear and Status, 40 of 64-bit Memory BAR[2+3] Read/Write 32-bits only

bit D31

D30 …

D25

D24 D23 D22 D21 D20 D19 D18

D17

D16

D15 …

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Name WDG UNUSED EXT1 EXT0 LDAC FOF FAF DTO DDONE ADCSTART ADCTRIG UNUSED enDACFHE enEXT1 enEXT0 enLDAC enFOF enFAF enDTO enDDONE enADCSTART enADCTRIG

Read IRQ Status to determine which/if any IRQs have fired (D23…D16), if the Watchdog has Barked (D31), and which IRQs are ena

bled (D9

…D0):