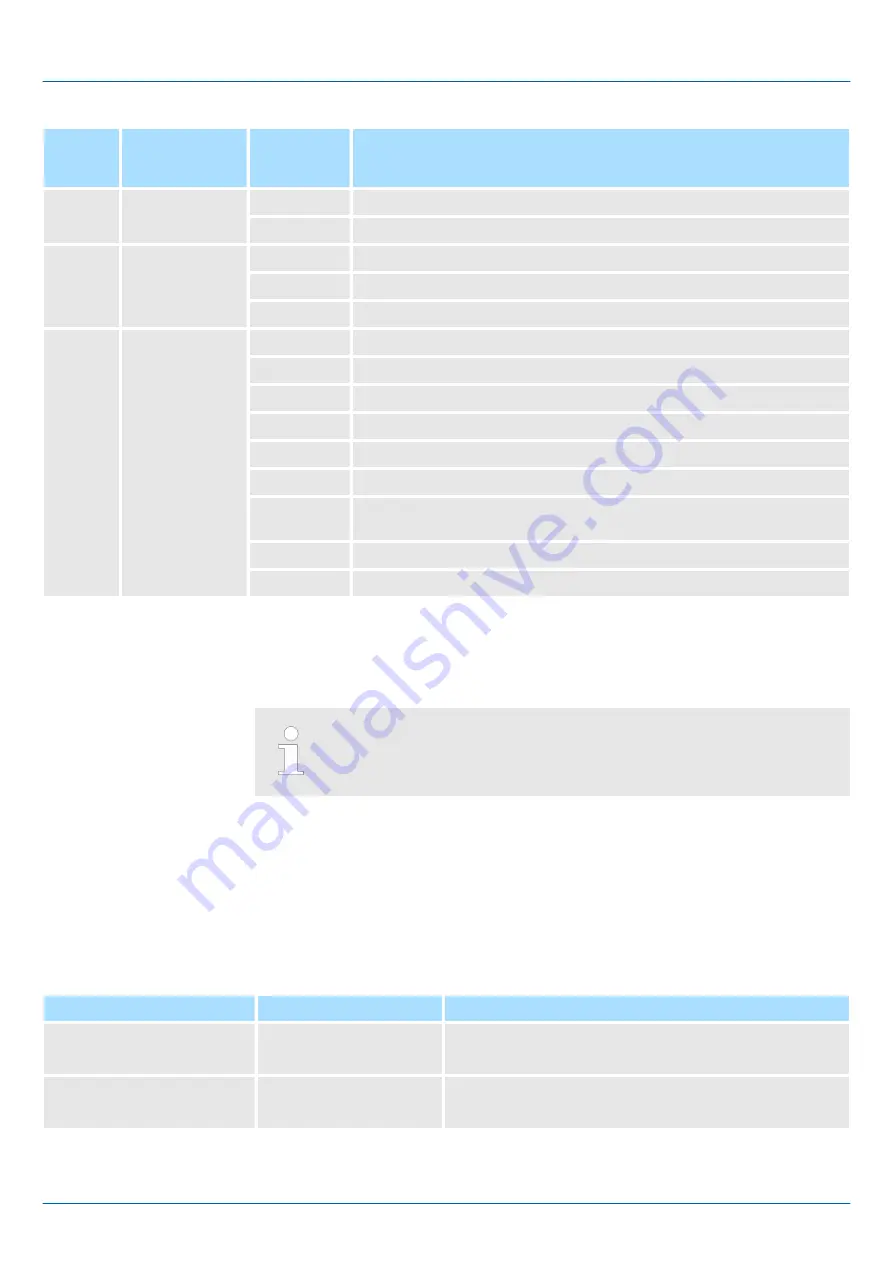

Bit no.

Explanation

Possible

values

(binary)

Description

0001

Automatic startup illegal, parameter modifications, etc. necessary

0111

Automatic startup permitted

11...8

Permissibility of

manual startup

0000

Manual startup illegal, memory request requested

0001

Manual startup illegal, parameter modifications, etc. necessary

0111

Manual startup permitted

7...0

Last valid inter-

vention or setting

of the automatic

startup at Pow-

erON

0000 0000

No startup

0000 0011

Restart triggered with mode selector

0000 0100

Restart triggered by command via MPI

0001 0000

Automatic restart after battery-backed PowerON

0001 0011

Restart triggered with mode selector; last PowerON battery-backed

0001 0100

Restart triggered by command via MPI; last PowerON battery-backed

0010 0000

Automatic restart after battery-backed PowerON (with memory reset by

system)

0010 0011

Restart triggered with mode selector last PowerON not battery-backed

0010 0100

Restart triggered by command via MPI last PowerON not battery-backed

6.4 Communication Interrupts

6.4.1 OB 55 - DP: Status Alarm - Status Interrupt

A status interrupt OB (OB 55) is only available for DP-V1 capable CPUs.

The CPU operating system calls OB 55 if a status interrupt was triggered via the slot of a

DP-V1 slave. This might be the case if a component (module) of a DP-V1 slaves changes

its operating mode, for example from RUN to STOP. For precise information on events

that trigger a status interrupt, refer to the documentation of the DP-V1 slave‘s manufac-

turer.

The following table describes the start information of the OB 55 with default names of the

variables and its data types:

Variable

Data type

Description

OB55_EV_CLASS

BYTE

Event class and identifiers:

11h: incoming event

OB55_STRT_INF

BYTE

55h: Status interrupt for DP

58h: Status interrupt for PROFINET IO

Description

Local data

VIPA SPEED7

Organization Blocks

Communication Interrupts > OB 55 - DP: Status Alarm - Status Interrupt

HB00 | OPL_SP7 | Operation list | en | 18-30

74