24

www.xilinx.com

ML505/ML506/ML507 Evaluation Platform

UG347 (v3.1.1) October 7, 2009

Chapter 1:

ML505/ML506/ML507 Evaluation Platform

R

Other Expansion I/O Connectors

In addition to the high-speed I/O paths, additional I/O signals and power connections are

available to support expansion cards plugged into the ML50

x

board. Fourteen I/O pins

from the general-purpose pushbutton switches and LEDs on the board are connected to

expansion connector J5. This permits additional I/Os to connect to the expansion

connector if the pushbutton switches and LEDs are not used. The connection also allows

the expansion card to utilize the pushbutton switches and LEDs on the board.

The expansion connector also allows the board's JTAG chain to be extended onto the

expansion card by setting jumper J21 accordingly.

The IIC bus on the board is also extended onto the expansion connector to allow additional

IIC devices to be bused together. If the expansion IIC bus is to be utilized, the user must

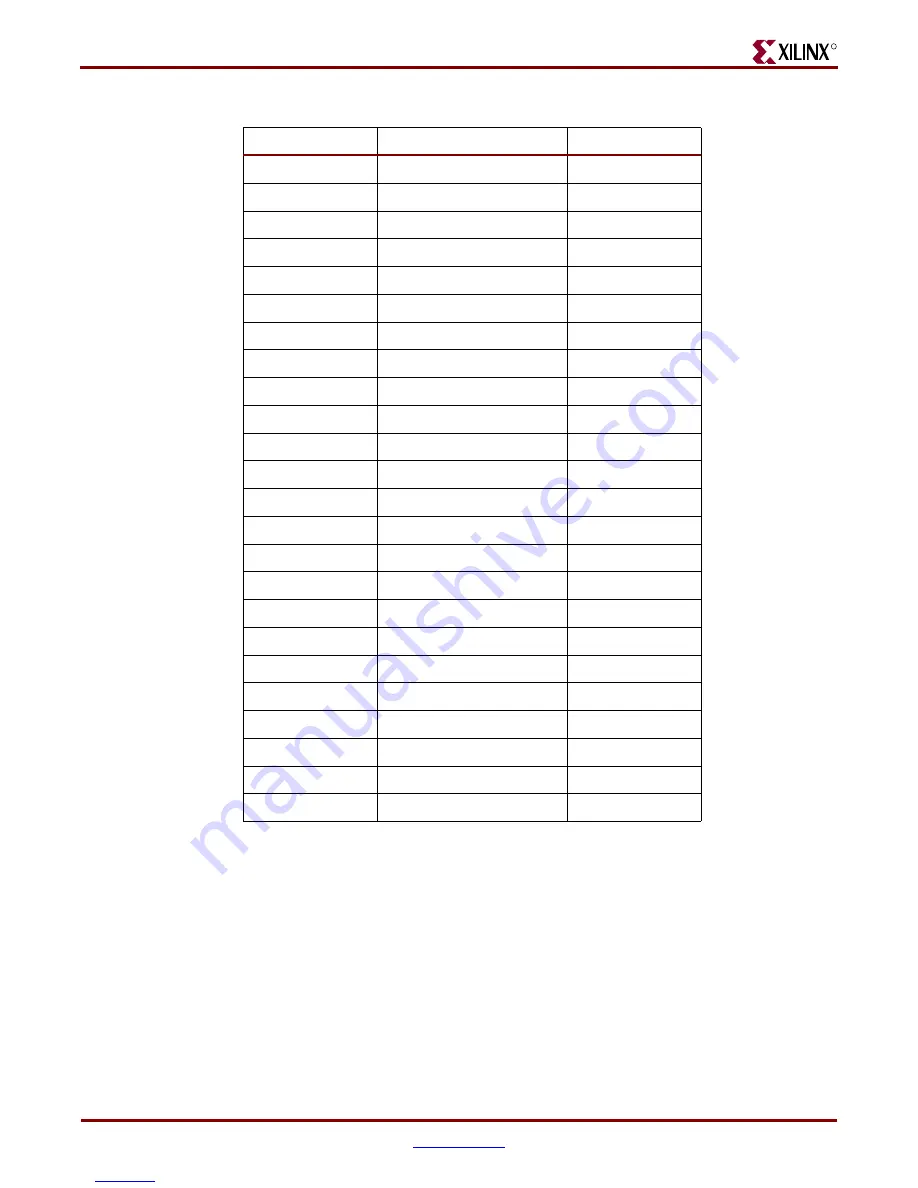

18

HDR1_18

L33

20

HDR1_20

M32

22

HDR1_22

P34

24

HDR1_24

N34

26

HDR1_26

AA34

28

HDR1_28

AD32

30

HDR1_30

Y34

32

HDR1_32

Y32

34

HDR1_34

W32

36

HDR1_36

AH34

38

HDR1_38

AE32

40

HDR1_40

AG32

42

HDR1_42

AH32

44

HDR1_44

AK34

46

HDR1_46

AK33

48

HDR1_48

AJ32

50

HDR1_50

AK32

52

HDR1_52

AL34

54

HDR1_54

AL33

56

HDR1_56

AM33

58

HDR1_58

AJ34

60

HDR1_60

AM32

62

HDR1_62

AN34

64

HDR1_64

AN33

Table 1-10:

Expansion I/O Single-Ended Connections (J6)

(Cont’d)

J6 Pin

Schematic Net Name

FPGA Pin

electronic components distributor