SLOU186F

–

AUGUST 2006

–

REVISED AUGUST 2010

5.3.3

Status Registers

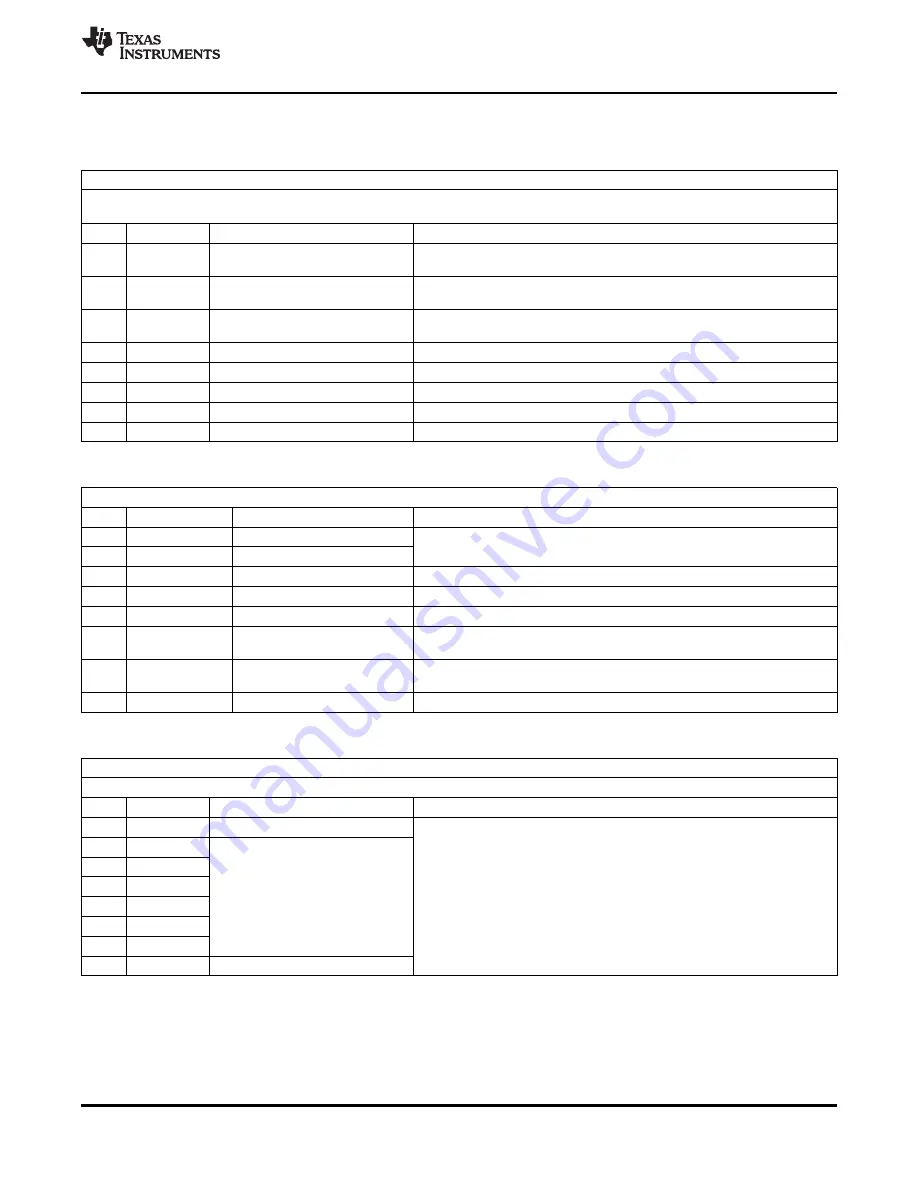

Table 5-22. IRQ Status Register (0Ch)

Displays the cause of IRQ and TX/RX status

Register default is set to 0x00 at POR = H or EN = L, and at each write to the ISO control register. It is also automatically reset at the end

of a read phase. The reset also removes the IRQ flag.

Bit

Bit Name

Function

Comments

B7

Irq_tx

IRQ set due to end of TX

Signals that TX is in progress. The flag is set at the start of TX but the

interrupt request is sent when TX is finished.

B6

Irg_srx

IRQ set due to RX start

Signals that RX SOF was received and RX is in progress. The flag is set at

the start of RX but the interrupt request is sent when RX is finished.

B5

Irq_fifo

Signals the FIFO is 1/3

>

FIFO

>

Signals FIFO high or low (less than 4 or more than 8)

2/3

B4

Irq_err1

CRC error

Indicates receive CRC error

B3

Irq_err2

Parity error

Indicates parity error

B2

Irq_err3

Byte framing or EOF error

Indicates framing error

B1

Irq_col

Collision error

For ISO14443A and ISO15693 single sub-carrier

B0

Irq_noresp

No-response interrupt

Signal to MCU that next slot command can be sent

Table 5-23. Collision Position and Interrupt Mask Register (0Dh)

Register default is set to 3E at POR = H and EN = L. Collision bits reset automatically after read operation.

Bit

Bit Name

Function

Comments

B7

Col9

Bit position of collision MSB

Supported: ISO15693, single sub-carrier, and ISO14443A

B6

Col8

Bit position of collision

B5

En_irq_fifo

Interrupt enable for FIFO

B4

En_irq_err1

Interrupt enable for CRC

B3

En_irq_err2

Interrupt enable for Parity

B2

En_irq_err3

Interrupt enable for Framing

error or EOF

B1

En_irq_col

Interrupt enable for collision

error

B0

En_irq_noresp

Enables no-response interrupt

Table 5-24. Collision Position (0Eh)

Displays the bit position of collision or error

Register default is set to 0x00 at POR = H and EN = L. Automatically reset after read operation.

Bit

Bit Name

Function

Comments

B7

Col7

Bit position of collision MSB

Supported is ISO15693, single sub-carrier, and ISO14443A

B6

Col6

In other protocols, it shows the bit position of error, either frame, SOF-EOF,

parity, or CRC error.

B5

Col5

B4

Col4

B3

Col3

B2

Col2

B1

Col1

B0

Col0

Bit position of collision LSB

Copyright

©

2006

–

2010, Texas Instruments Incorporated

System Description

31

focus.ti.com: