b7

b6

b5

b4

b3

b2

b1

b0

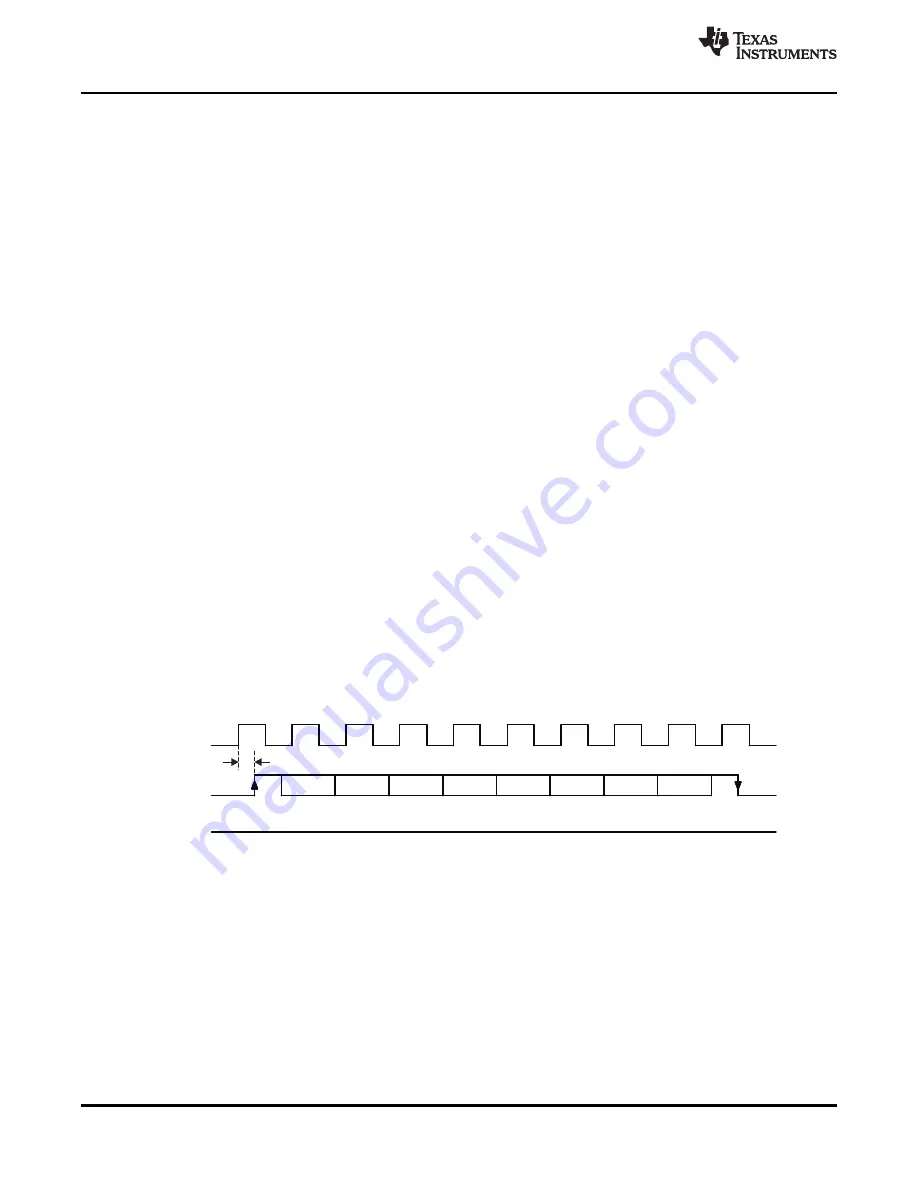

Start

Condition

Stop

Condition

SCLK

Data IN

Data Out

50 ns

SLOU186F

–

AUGUST 2006

–

REVISED AUGUST 2010

5.7

Serial Interface Communication

When an SPI interface is required, parallel I/O pins, I/O_2, I/O_1, and I/O_0, must be hard wired

according to Table 5-31. On power up, the reader looks for the status of these pins; if they are not the

same (not all high, or not all low), the reader enters into one of two possible SPI modes.

The serial communications work in the same manner as the parallel communications with respect to the

FIFO, except for the following condition. On receiving an IRQ from the reader, the MCU reads the reader's

IRQ register to determine how to service the reader. After this, the MCU must to do a dummy read to clear

the reader's IRQ status register. The dummy read is required in SPI mode because the reader's IRQ

status register needs an additional clock cycle to clear the register. This is not required in parallel mode

because the additional clock cycle is included in the Stop condition.

A procedure for a dummy read is as follows:

A. Starting the dummy read:

(a) When using slave select (SS): set SS bit low.

(b) When not using SS: start condition is when SCLK is high (See

).

B. Send address word to IRQ status register (0Ch) with read and continuous address mode bits set to 1

(See

C. Read 1 byte (8 bits) from IRQ status register (0Ch).

D. Dummy-read 1 byte from register 0Dh (collision position and interrupt mask).

E. Stopping the dummy read:

(a) When using slave select (SS): set SS bit high.

(b) When not using SS: stop condition when SCLK is high (See

).

5.7.1

SPI Interface Without SS* (Slave Select) Pin

The serial interface without the slave select pin must use delimiters for the start and stop conditions.

Between these delimiters, the address, data, and command words can be transferred. All words must be 8

bits long with MSB transmitted first.

Figure 5-8. Serial

–

SPI Interface Communication (No SS* Pin)

In this mode, a rising edge on data-in (I/O_7, pin 24) while SCLK is high resets the serial interface and

prepares it to receive data. Data-in can change only when SCLK is low and is taken by the reader on the

SCLK rising edge. Communication is terminated by the stop condition when the data-in falling edge occurs

during a high SCLK period.

5.7.2

SPI Interface With SS* (Slave Select) Pin

The serial interface is in reset while the SS* signal is high. Serial data-in (MOSI) changes on the falling

edge, and is validated in the reader on the rising edge, as shown in

. Communication is

terminated when the SS* signal goes high.

All words must be 8 bits long with the MSB transmitted first.

40

System Description

Copyright

©

2006

–

2010, Texas Instruments Incorporated

focus.ti.com: