GND

GND

GND

GND

GND

TDI

TDO

TRST

TMS

TCK

JTAG

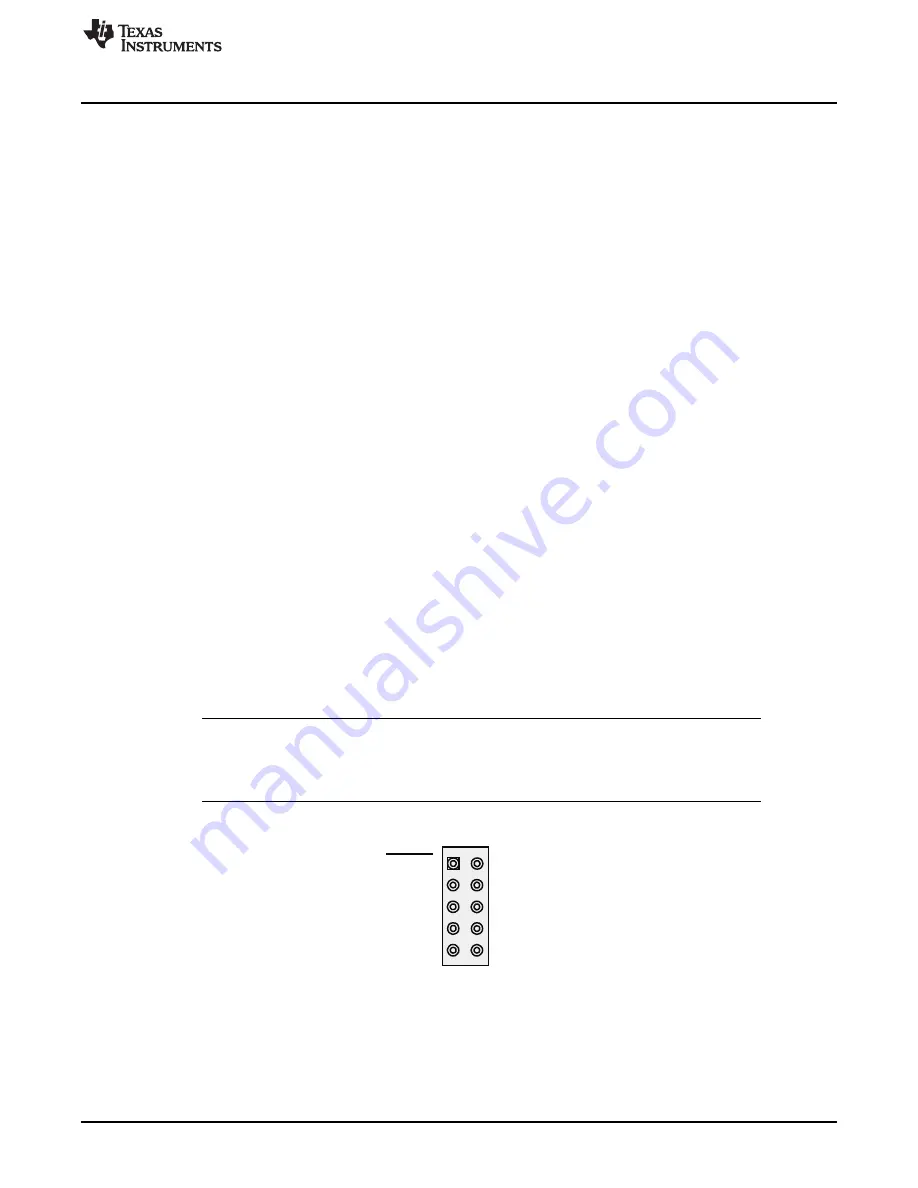

JMP35

www.ti.com

JTAG

9

JTAG

The EVM also provides a separate connector to support the full five-pin JTAG interface of the TLK6002

with onboard level shifters to be compatible with most standard JTAG Control Interfaces to be used for

manufacturing tests. Pullup resistors on the 3.3-V (header) side of the level shifter are not installed by TI

but can be installed if an open-drain type of controller is used which requires the use of external pullup

resistors.

TDI: JTAG Input Data. TDI is used to serially shift test data and test instructions into the device

during the operation of the test port. In system applications where JTAG is not implemented, this

input signal can be left floating. During pin-based power down (PD_TRXA_N and PD_TRXB_N

asserted low), this pin is not pulled up. During register-based power down (1.15 asserted high for

both channels), this pin is pulled up normally.

TDO: JTAG Output Data. TDO is used to serially shift test data and test instructions out of the

device during operation of the test port. When the JTAG port is not in use, TDO is in a

high-impedance state. During device reset (RESET_N asserted low), this pin is floating. During

pin-based power down (PD_TRXA_N and PD_TRXB_N asserted low), this pin is floating. During

register-based power down (1.15 asserted high on both channels), this pin is floating.

TMS: JTAG Mode Select. TMS is used to control the state of the internal test-port controller. In

system applications where JTAG is not implemented, this input signal can be left unconnected.

During pin-based power down (PD_TRXA_N and PD_TRXB_N asserted low), this pin is not

pulled up. During register-based power down (1.15 asserted high both channels), this pin is

pulled up normally.

TCK: JTAG Clock. TCK is used to clock state information and test data into and out of the device

during boundary scan operation. In system applications where JTAG is not implemented, this

input signal must be grounded.

TRST_N: JTAG Test Reset. TRST_N is used to reset the JTAG logic into system operational

mode. This input can be left unconnected in the application and is pulled down internally,

disabling the JTAG circuitry. If JTAG is implemented on the application board, this signal must be

de-asserted (high) during JTAG system testing, and otherwise asserted (low) during normal

operation mode. During pin-based power down (PD_TRXA_N and PD_TRXB_N asserted low),

this pin is not pulled down. During register-based power down (1.15 asserted high on both

channels), this pin is pulled down normally.

NOTE:

TRST_N must be tied low when the JTAG port is not in use and during normal operation of

the port as shown in

Figure 11

because an external pullup resistor is provided. If you have

no need to use the JTAG port, removing resistor R423 allows the internal pulldown to disable

the circuitry and installing resistor R426 provides an external pulldown on this pin.

Figure 11. TLK6002 EVM JTAG Connector (JMP35)

19

SLLU132 – October 2010

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Evaluation Module

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated