<Document ID>

© NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 0.11 — 25 January 2007

10 of 230

NXP Semiconductors

UOC-TOP-64 N1 series

Signal processor for CRT TV

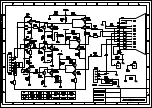

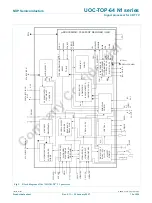

Fig 2.

Block diagram of the “MONO-90” TV processor

V-

D

R

IV

E

EH

T

O

AM DE

MO

DU

LA

TO

R

V

ISI

ON

I

F/A

GC/

A

FC

PLL DEMOD.

V

IDE

O A

M

P.

S

OUN

D TRA

P

GRO

U

P DE

LA

Y

V

IDE

O SWI

T

CH

V

IDE

O I

D

EN

T.

V

IDE

O FIL

T

E

R

S

DECO

DE

R

PAL/

SECAM/NTSC

BASE-BAND

DE

LA

Y LI

NE

H/V SYNC SEP.

H-OSC.

+ PLL

2

nd

LO

OP

H-SH

IFT

H-

D

R

IV

E

VE

RTICA

L

AG

COU

T

VI

FI

N

H-

O

U

T

RGB/

YP

R

P

B

CON.

BRI

RO

GO

BO

BLKIN/VGUARD

RGB CONTROL

O

SD/

TE

XT

I

N

SE

RT

CCC/

BLACK ADJ.

WH

IT

E

-P. A

D

J.

CONTR/BRIGHTN

RGB MA

TRIX

H/

V

REF

Y

D

E

L

AY

AD

J.

SATURATION

CVBS2/

Y

2

YSY

N

C

IFVO

/SV

O

SO

UN

D PL

L

DE

EMPH

ASI

S

B3/

BLACK-STRETCH

BCLIN

CLK

GE

NE

RAT

ION

I

2

C-BUS

///

///

//

//

//

CSO

CSI

H/

VD

ISPO

H/

VD

ISPI

CLKI

CLKO

IREFRGB

R/G/B

VD

S

INS.

CIRN

CORB

SDA/SCL

IREF

IREFO

CVBSREF

CVBS I

N

RESET

TMSE

L

µ

-PROCESSOR / TELETEXT DECODER / OSD

AM

A

UDI

O

SE

LE

CT

SCART/

C

INCH

LS/SCART/

C

INCH

L

L

S AU

DI

O

OU

TPU

T

VO

LU

ME/

A

V

L

SA

T

CONTROL

IN

P

B

-3

FM

SO

UN

D-

D

O

W

N

-

MIXER

SW

IT

C

H

-OU

T

SECAM

PEAKING

R3/

G3

/

P

R

-3/

Y-

3

C2/

C

3/

C4

CVBS3/ Y3

C2/C3/C4/

CVBS4/Y4

I/O

s

A

V

L/

SS

IF

OU

T/

FM

DEMOUT

AVL

COR

ING

GAM

M

A

C

O

NTROL