<Document ID>

© NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 0.11 — 25 January 2007

4 of 230

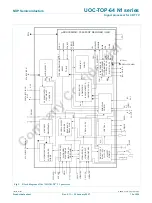

NXP Semiconductors

UOC-TOP-64 N1 series

Signal processor for CRT TV

2.2 Micro-Controller

80C51 m-controller core standard instruction set and timing

0.9766 ms machine cycle

maximum of 80 k x 8-bit late programmed ROM

maximum of 3 k x 8-bit Auxiliary RAM

I

2

C byte level bus interface.

Interrupt controller for individual enable/disable with two level priority

Two 16-bit Timer/Counter registers

One 24-bit Timer (16-bit timer with 8-bit Pre-scaler)

16-bit Data pointer

WatchDog timer

Auxiliary RAM page pointer

Stand-by, Idle and Power Down modes

Up to 13 general-purpose I/O pins

14 bits PWM for Voltage Synthesis Tuning

8-bit A/D converter with 4 multiplexed inputs

4 PWM (6-bits) outputs for analogue control functions

2.3 Data Capture (Teletext and Closed Caption devices)

Text memory for 1 page

Inventory of transmitted Teletext pages stored in the Transmitted Page Table (TPT)

and Subtitle Page Table (SPT)

Data Capture for US Closed Caption

Data Capture for 525/625 line WST, VPS (PDC system A) and 625 line Wide Screen

Signalling (WSS) bit decoding

Automatic selection between 525 WST/625 WST

Automatic selection between 625 WST/VPS on line 16 of VBI

Real-time capture and decoding for WST Teletext in Hardware, to enable optimized

m-processor throughput

Automatic detection of FASTEXT transmission

Real-time packet 26 engine in Hardware for processing accented, G2 and G3

characters

Signal quality detector for video and WST/VPS data types

Comprehensive teletext language coverage

Vertical Blanking Interval (VBI) data capture of WST data