Obsolete Product(s) - Obsolete Product(s)

3/33

L6917B

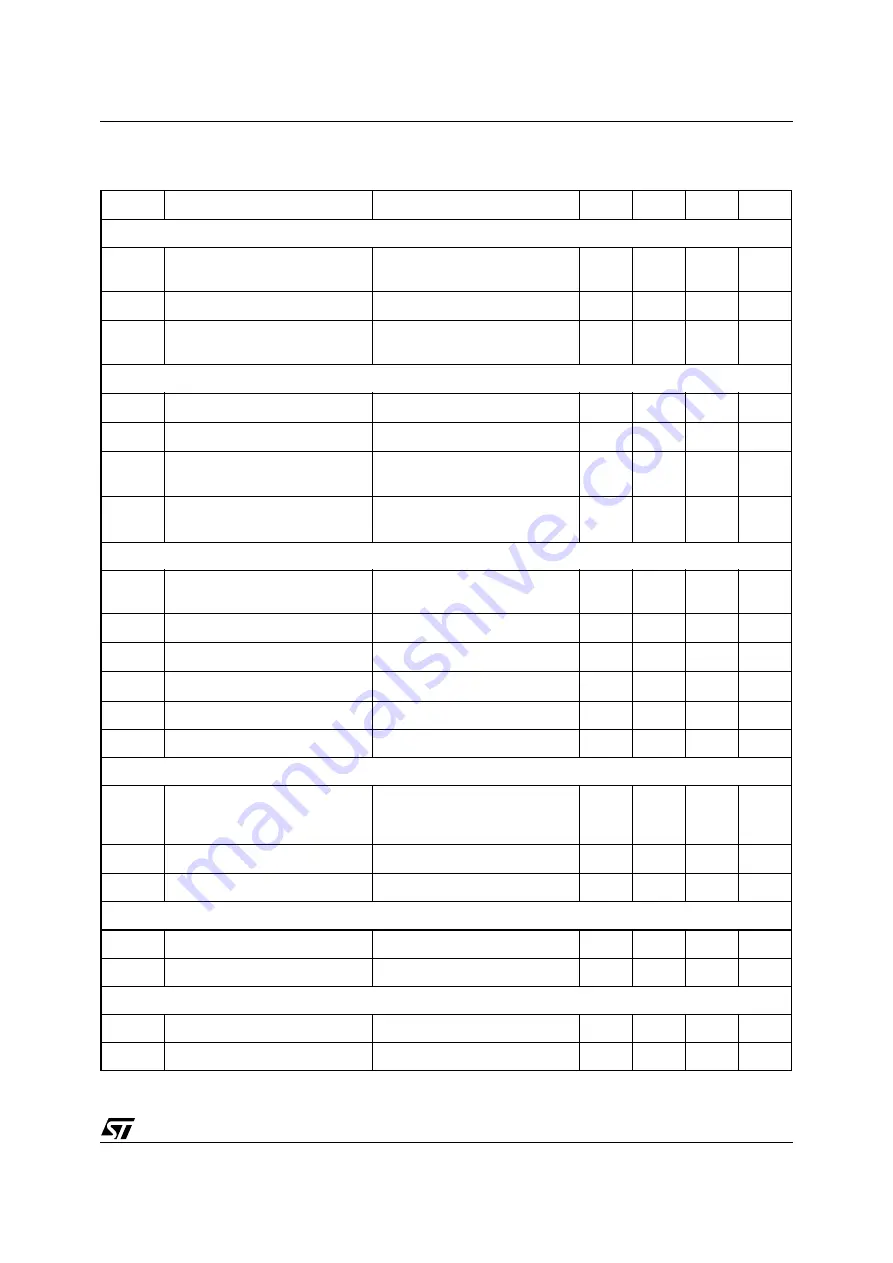

ELECTRICAL CHARACTERISTICS

V

CC

= 12V ±10%, T

J

= 0 to 70°C unless otherwise specified

Symbol

Parameter

Test Condition

Min

Typ

Max

Unit

Vcc SUPPLY CURRENT

I

CC

Vcc supply current

HGATEx and LGATEx open

V

CCDR

=V

BOOT

=12V

7.5

10

12.5

mA

I

CCDR

V

CCDR

supply current

LGATEx open; V

CCDR

=12V

2

3

4

mA

I

BOOTx

Boot supply current

HGATEx open; PHASEx to PGND

V

CC

=V

BOOT

=12V

0.5

1

1.5

mA

POWER-ON

Turn-On V

CC

threshold

V

CC

Rising; V

CCDR

=5V

7.8

9

10.2

V

Turn-Off V

CC

threshold

V

CC

Falling; V

CCDR

=5V

6.5

7.5

8.5

V

Turn-On V

CCDR

Threshold

V

CCDR

Rising

V

CC

=12V

4.2

4.4

4.6

V

Turn-Off V

CCDR

Threshold

V

CCDR

Falling

V

CC

=12V

4.0

4.2

4.4

V

OSCILLATOR/INHIBIT/FAULT

f

OSC

Initial Accuracy

OSC = OPEN

OSC = OPEN; Tj=0

°

C to 125

°

C

278

270

300

322

330

kHz

kHz

f

OSC,Rosc

Total Accuracy

R

T

to GND=74k

Ω

450

500

550

kHz

INH

Inhibit threshold

I

SINK

=5mA

0.8

0.85

0.9

V

d

MAX

Maximum duty cycle

OSC = OPEN

70

75

%

∆

Vosc

Ramp Amplitude

1.8

2

2.2

V

FAULT

Voltage at pin OSC

OVP or UVP Active

4.75

5.0

5.25

V

REFERENCE AND DAC

Output Voltage

Accuracy

VID0, VID1, VID2, VID3, VID4

see Table1;

FBR = V

OUT

; FBG = GND

-0.8

-

0.8

%

I

DAC

VID pull-up Current

VIDx = GND

4

5

6

µ

A

VID pull-up Voltage

VIDx = OPEN

3.1

-

3.4

V

ERROR AMPLIFIER

DC Gain

80

dB

SR

Slew-Rate

COMP=10pF

15

V/

µ

s

DIFFERENTIAL AMPLIFIER (REMOTE BUFFER)

DC Gain

1

V/V

CMRR

Common Mode Rejection Ratio

40

dB

Obsolete Product(s) - Obsolete Product(s)