PulseBlasterESR-PRO-200-cPCI

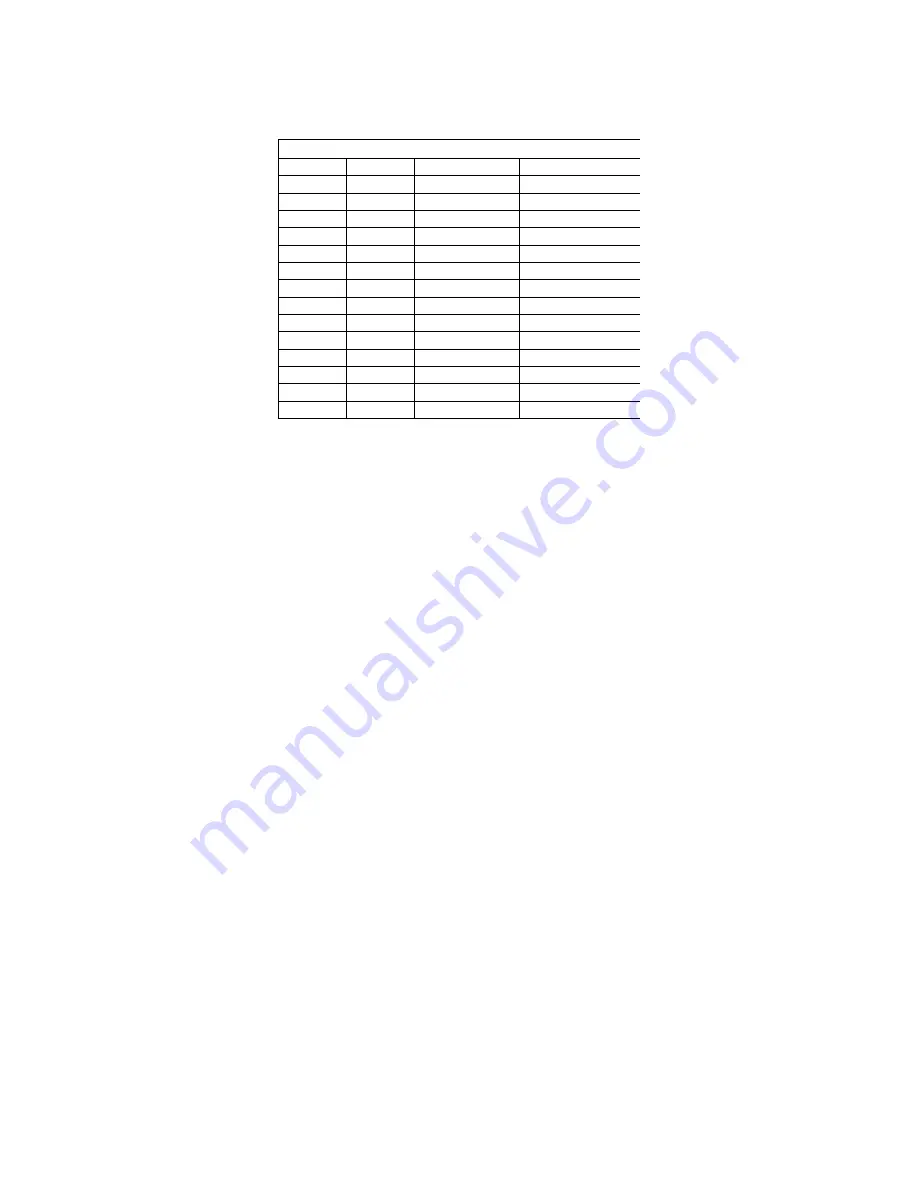

The PulseBlaster device features four extra output signals, called "Status" signals, which can tell the user

or an external device what state the PulseBlaster device is in. Pin assignments for these signals are shown in

the table above. The status bits are defined as follows:

•

Stopped

◦

Driven high when the PulseBlaster device has encountered a STOP OpCode during program

execution.

•

Reset

◦

Driven low when the PulseBlaster device is in a RESET state. The device must be reprogrammed

before code execution can begin again.

•

Running

◦

Driven high when the PulseBlaster device is executing a program. This pin is low when the

PulseBlaster enters either a reset or idle state.

•

Waiting

◦

Driven high when the PulseBlaster device has encountered a WAIT OpCode. Activating a trigger

(either hardware or software) will resume operation.

19

2017/01/24

Pin Assignments

Pin#

Flag0..11

Flag12..23

Flag24..35

1

Bit 0

Bit 12

Stopped

2

Bit 1

Bit 13

Reset

3

Bit 2

Bit 14

Running

4

Bit 3

Bit 15

Waiting

5

Bit 4

Bit 16

Unused

6

Bit 5

Bit 17

Unused

7

Bit 6

Bit 18

Unused

8

Bit 7

Bit 19

Unused

9

Bit 8

Bit 20

Unused

10

Bit 9

Bit 21

Unused

11

Bit 10

Bit 22

Unused

12

Bit 11

Bit 23

Unused

13

Unused

Unused

Unused

14-26

Ground

Ground

Ground

Table 1:

IDC header pinout description. Every bit of

the Output Pattern and Control field correspond to a

channel. Pins 1 – 4 on IDC header “Flag24...35” are

status bits. They allow the user or an external device

to monitor the state of the PulseBlaster device.