4-9

WLL-CA55

109

110

115

120

125

130

135

140

144

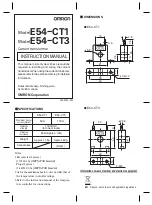

FIXED POINT DIGITAL SIGNAL PROCESSOR

—TOP VIEW—

72

70

65

60

55

50

45

40

37

108

105

100

95

90

85

80

75

73

1

5

10

15

20

25

30

35 36

TMS320VC5409APGE16 (TI)

NJM2772V(TE2) (JRC)

—

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I

—

—

—

I

I

I

O

O

O

O

O

O

O

O

O

O

I

I

I

—

—

I

I/O

GND

A22

GND

V

CC

A10

HD7

A11

A12

A13

A14

A15

V

CC

HAS

GND

GND

V

CC

HCS

HR/

W

READY

PS

DS

IS

R/

W

MSTRB

IOSTRB

MSC

XF

HOLDA

IAQ

HOLD

BIO

MP/

MC

V

CC

GND

BDR1

BFSR1

PIN

NO.

I/O

SIGNAL

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

—

I/O

I

—

I/O

I/O

I/O

I/O

I

I

I

I/O

I/O

—

O

—

I/O

I/O

O

—

—

I/O

O

O

O

I

I

I

I

I

I

—

I/O

—

I/O

—

GND

BCLKR1

HCNTL0

GND

BCLKR0

BCLKR2

BFSR0

BFSR2

BDR0

HCNTL1

BDR2

BCLKX0

BCLKX2

GND

HINT

V

CC

BFSX0

BFSX2

HRDY

V

CC

GND

HD0

BDX0

BDX2

IACK

HBIL

NMI

INT0

INT1

INT2

INT3

V

CC

HD1

GND

BCLKX1

GND

PIN

NO.

I/O

SIGNAL

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

I/O

O

—

—

I

I

I

I

I/O

O

I/O

I/O

O

I

I

I

I

—

—

I

—

O

I/O

O

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

BFSX1

BDX1

V

CC

GND

CLKMD1

CLKMD2

CLKMD3

HPI16

HD2

TOUT

EMU0

EMU1/

OFF

TDO

TDI

TRST

TCK

TMS

GND

V

CC

HPIENA

GND

CLKOUT

HD3

X1

X2/CLKIN

RS

D0

D1

D2

D3

D4

D5

A16

GND

A17

A18

PIN

NO.

I/O

SIGNAL

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I

—

I

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

—

A19

A20

GND

V

CC

D6

D7

D8

D9

D10

D11

D12

HD4

D13

D14

D15

HD5

V

CC

GND

HDS1

GND

HDS2

V

CC

A0

A1

A2

A3

HD6

A4

A5

A6

A7

A8

A9

V

CC

A21

GND

PIN

NO.

I/O

SIGNAL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

INPUTS

BIO

BDR0 - BDR2

CLKMD1 - CLKMD3

HAS

HBIL

HCNTL0, HCNTL1

HCS

HDS1

,

HDS2

HOLD

HR/

W

HPI16

HPIENA

INT0

-

INT3

MP/

MC

NMI

RS

READY

TCK

TDI

TMS

TRST

X2/CLKIN

OUTPUTS

BDX0 - BDX2

CLKOUT

DS

HINT

HOLDA

HRDY

IACK

IAQ

IOSTRB

IS

MSC

MSTRB

PS

R/

W

TDO

TOUT

X1

XF

INPUTS/OUTPUTS

A0 - A22

BCLKR0 - BCLKR2

BCLKX0 - BCLKX2

BFSR0 - BFSR2

BFSX0 - BFSX2

D0 - D15

EMU0

EMU1/

OFF

HD0 - HD7

: BRANCH CONTROL

: SERIAL DATA RECEIVE

: CLOCK MODE SELECT

: ADDRESS STROBE

: BYTE IDENTIFICATION

: CONTROL

: CHIP SELECT

: DATA STROBE

: HOLD

: READ/WRITE

: HOI16 MODE SELECTION

: HP1 MODULE SELECT

: EXTERNAL USER INTERRUPT

: MICROPROCESSOR/MICROCOMPUTER

MODE SELECT

: NON-MASKABLE INTERRUPT

: RESET

: DATA READY

: TEST CLOCK

: TEST DATA INPUT

: TEST MODE SELECT

: TEST RESET

: CLOCK/ OSCILLATOR

: SERIAL DATA TRANSMIT

: CLOCK

: DATA SELECT

: INTERRUPT

: HOLD ACKNOWLEDGE

: READY

: INTERRUPT ACKNOWLEDGE

: INSTRUCTION ACQUISITION

: I/O STROBE

: I/O SPACE SELECT

: MICROSTATE COMPLETE

: MEMORY STROBE

: PROGRAM SELECT

: READ/WRITE

: TEST DATA

: TIMER

: OSCILLATOR

: EXTERNAL FLAG

: ADDRESS

: RECEIVE CLOCK

: TRANSMIT CLOCK

: FRAME SYNCHRONIZATION PULSE FOR RECEIVE

: FRAME SYNCHRONIZATION PULSE FOR TRANSMIT I/O

: DATA

: EMULATOR 0 PIN

: EMULATOR 1 PIN/ DISABLE ALL OUTPUT

: PARALLEL BIDIRECTIONAL DATA

HEADPHONE AMPLIFIER

—TOP VIEW—

STBY

INA

CENTER SW

VREF

BEEP

INB

MUTE

1

2

3

4

5

6

7

14

13

12

11

10

9

8

DNC

OUTA

V

CC

OUTC

GND

OUTB

MUTE TC

: BEEP SIGNAL

: AMPLIFIER C ON/OFF CONTROL

: AMPLIFIER A

: AMPLIFIER B

: MUTE CONTROL

: MUTE TIMING CONTROL

: STANDBY CONTROL

: REFERENCE VOLTAGE

: AMPLIFIER A

: AMPLIFIER B

: AMPLIFIER C

: NO CONNECTION

INPUTS

BEEP

CENTER SW

INA

INB

MUTE

MUTE TC

STBY

VREF

OUTPUTS

OUTA

OUTB

OUTC

OTHER

DNC

STBY

1

+

+

VREF

AMP-A

AMP-C

AMP-B

INA

2

3

4

5

6

7

CENTER SW

VREF

BEEP

INB

MUTE

13

11

9

8

MUTE TC

OUTB

OUTC

OUTA