7-3

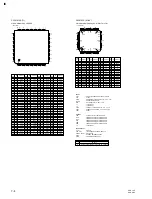

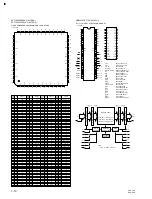

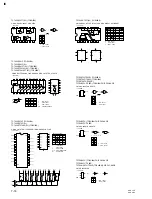

HSR-1/1P

HSR-2/2P

IC

IC

1

2

3

4

CS

SK

DI

DO

8

7

6

5

RDY/

BUSY

RESET

INPUT

CS

DI

RESET

SK

: CHIP SELECT

: SERIAL DATA

: RESET

: SERIAL DATA CLOCK

OUTPUT

DO

RDY/

BUSY

: SERIAL DATA

: READY/

BUSY

V

DD

GND

4

7

3

2

1

DI

SK

CS

DO

RDY/

BUSY

6

RESET

C-MOS 8 K (512

x

16)-BIT SERIAL EEPROM

—TOP VIEW—

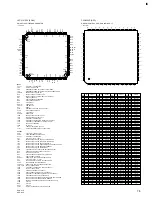

DECODER

R/W AMP

AND

AUTO ERASE

EEPROM

8,192 BITS

(512

x

16)

VPP

SWITCHER

DATA

REGISTER

INSTRUCTION

DECODER,

CONTROLLER

AND

CLOCK

GENERATOR

ADDRESS

BUFFER

VPP

GENERATOR

4

DO

7

RDY/BUSY

16

16

16

INSTRUCTION

REGISTER

8

8

V REF

3

DI

2

SK

1

CS

6

RESET

IN

OUT

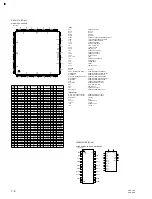

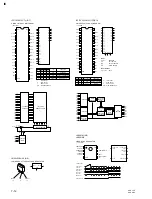

2

GND

1

3

1

3

(2)

2

POSITIVE VOLTAGE REGULATOR

8

7

6

5

1

2

GND

GND

SW

OUT

CONT

IN2

IN1

V

EE

V

CC

3

4

IN1

IN2

CONT

OUT

1

3

5

7

VIDEO SIGNAL SWITCH

—TOP VIEW—

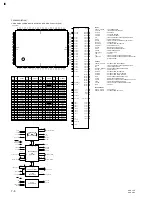

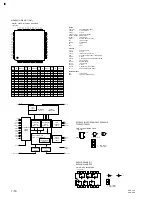

25

26

27

28

29

30

31

32

DGND

DGND

AGND

AGND

AV

DD

AV

DD

AV

DD

DV

DD

DV

DD

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

17

18

21

12

25

24

29

27

26

15

14

13

VRTS

VRT

V IN

VRBS

VRB

CLE

CCP

V REF

PW

SYNC

SEL

OE

30

D0

D1

D2

D3

D4

D5

D6

D7

1

2

3

4

5

6

7

8

PIN

NO.

I/O

O

O

O

O

O

O

O

O

—

—

—

I

I

I

I

—

D0(LSB)

D1

D2

D3

D4

D5

D6

D7(MSB)

NC

DV

DD

DV

DD

CLK

SEL

SYNC

PW

AV

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

SIGNAL

PIN

NO.

I/O

I

I

—

—

I

—

—

I

I

I

I

—

I

I

—

—

VRTS

VRT

AV

DD

AV

DD

V IN

AGND

AGND

VRB

VRBS

VREF

CCP

DGND

CLE

OE

DGND

NC

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

SIGNAL

INPUT

CCP

CLE

CLK

CLP

OE

PW

SEL

SYNC

V IN

VRB

VRBS

VREF

VRT

VRTS

OUTPUT

D0 - D7

; CLAMP CONTROL VOLTAGE

FOR INTEGRATOR

; CLAMP ENABLE

; CLOCK

; CLAMP PULSE

; OUTPUT ENABLE

; PULSE WIDTH FOR MONO MULTI

; TRIGGER SELECT

; TRIGGER PULSE FOR MONO MULTI

VIBRATOR

; ANALOG

; REFERENCE VOLTAGE (BOTTOM)

; SELF REFERENCE VOLTAGE SHORT

(

+

0.5 V/BOTTOM)

; VOLTAGE REFERENCE FOR CLAMP

; REFERENCE VOLTAGE (TOP)

; SELF REFERENCE VOLTAGE SHORT

(

+

2.6 V/TOP)

; DATA

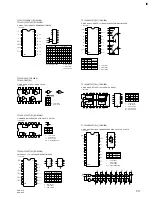

C-MOS 8-BIT 20MSPS VIDEO A/D CONVERTER

—TOP VIEW—

LOWER

DATA

LATCH

1

2

3

4

30

D0

(LSB)

D1

D2

D3

OE

LOWER

ENCODER

(4-BIT)

LOWER

SAMPLING

COMPARATOR

(4-BIT)

REFERENCE

SUPPLY

MONO MULTI

VIBRATOR

25

24

23

22

21

19

18

17

VRBS

VRB

AGND

AGND

V IN

AV

DD

VRT

VRTS

LOWER

SAMPLING

COMPARATOR

(4-BIT)

UPPER

SAMPLING

COMPARATOR

(4-BIT)

LOWER

ENCODER

(4-BIT)

UPPER

ENCODER

(4-BIT)

D4

D5

D6

D7

(MSB)

UPPER

DATA

LATCH

5

6

7

8

12

29

27

26

CLK

CLE

CCP

V REF

CLOCK

GENERATOR

_

+

15

14

13

PW

SYNC

SEL

AK6480AM-E2 (ASAHI KASEI)

BA033FP (ROHM)

BA033FP-E2

CXA1450M-TH (SONY)

CXD1176Q (SONY)

CXD1176Q-T4

Summary of Contents for HSRA-11

Page 6: ......

Page 74: ......

Page 84: ...9 10 9 10 HSR 1 1P HSR 2 2P ...

Page 91: ......

Page 98: ......

Page 109: ......

Page 111: ...10 15 10 15 HSR 1 1P HSR 2 2P CM 56 CM 56 CM 56 B SIDE SUFFIX 11 ...

Page 112: ...10 16 10 16 HSR 1 1P HSR 2 2P ...

Page 115: ...10 19 10 19 HSR 1 1P HSR 2 2P JC 19 C JC 19 C JC 19 C B SIDE SUFFIX 21 ...

Page 116: ...10 20 10 20 HSR 1 1P HSR 2 2P RP 228 RP 228 RP 228 A SIDE SUFFIX 11 ...

Page 118: ......

Page 141: ...2 3 4 5 I J K L M N O P 11 13 b1 11 13 b1 HSR 1 1P HSR 2 2P 1 ...

Page 166: ...2 3 4 5 A B C D E F G H 11 32 b 11 32 b HSR 1 1P HSR 2 2P 1 ...

Page 180: ...2 3 4 5 A B C D E F G H 11 32 a 11 32 a HSR 1 1P HSR 2 2P 1 ...

Page 188: ...2 3 4 5 A B C D E F G H 11 40 11 40 HSR 1 1P HSR 2 2P 1 ...

Page 204: ...11 56 11 56 HSR 1 1P HSR 2 2P JC 19 C 8 9 JC 19 C 8 9 ...

Page 221: ...2 3 4 5 I J K L M N O P 11 73 b 11 73 b HSR 1 1P HSR 2 2P 1 ...

Page 226: ......