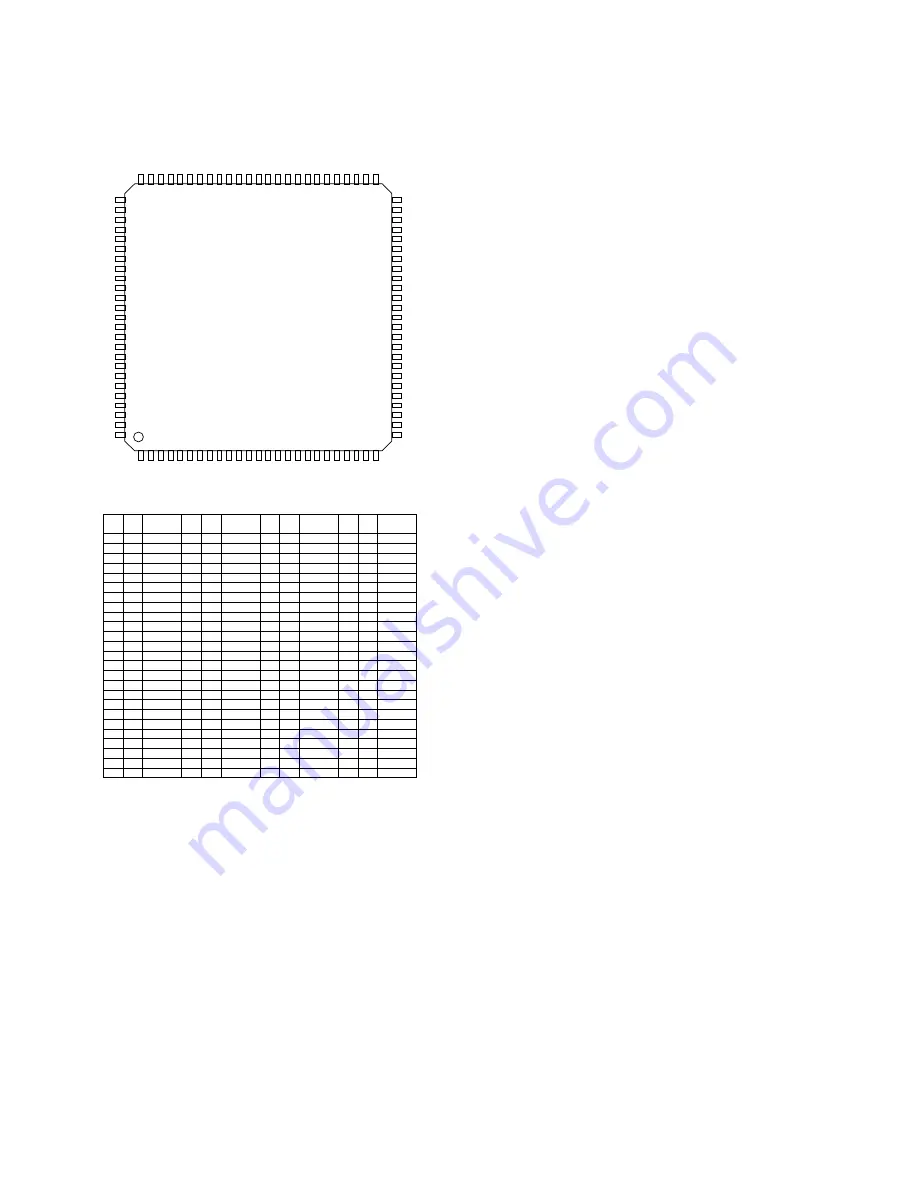

7-7

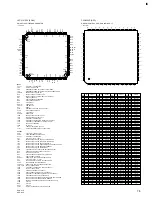

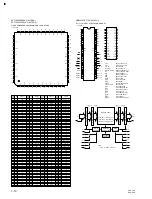

HSR-1/1P

HSR-2/2P

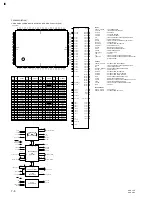

IC

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

GND

V

DD

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

V

DDS

GND

GND

V

DD

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

V

DD

GND

GND

GND

NC

NC

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

NC

NC

GND

GND

V

DD

GND

GND

C-MOS DIGITAL ENCODE/DECODE

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

I

I

—

I

O

—

I

I

I

I

I

I

I

I

—

I

I

I

I

I

I

—

—

—

—

TMODE

SD

V

DD

RTST

FERR

GND

PH1

HRED

SRED

RMTH2

RMTH1

RMTH0

PMTH1

PMTH0

GND

IMA

ATH1

ATH0

RMOD

DIG

FSTA

GND

NC

NC

NC

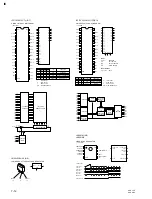

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

O

I

—

I

I

I

I

I

I

I

I

I

I

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

RDT

DORZ

V

DD

TDON

DRET

EACT0

EACT1

EASEL

EQNM0

EQNM1

EQNM2

EQNM3

EQSEL

TBP

GND

TDT0

TDT1

TDT2

TDT3

TDT4

TDT5

TDT6

TDT7

TDT8

TDT9

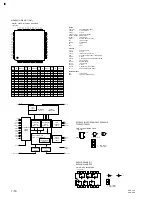

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

—

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

O

I

—

—

—

GND

GND

V

DD

DDT0

DDT1

DDT2

DDT3

DDT4

DDT5

DDT6

DDT7

DDT8

DDT9

DDT10

GND

DDT11

DDT12

DDT13

DDT14

DDT15

DOBUP

DIBUP

GND

NC

NC

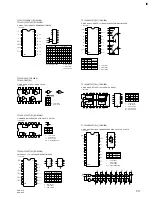

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

I

I

—

I

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I

I

I

I

I

I

O

I

I

TRCK

CIBUP

V

DDS

TTCK

GND

VDT7

VDT6

VDT5

VDT4

VDT3

VDT2

VDT1

VDT0

VBUP

GND

V

DD

RST

PS

REC

TRST

TCK

TMS

TDO

TDI

SMODE

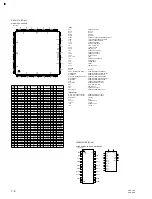

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

INPUT

ATH1, ATH0

CIBUP

DIBUP

DIG

DORZ

DRET

EACT0, EACT1

EASEL

EQNM0 - EQNM3

EQSEL

FSTA

HRED

IMA

PH1

PMTH0, PMTH1

PS

REC

RMOD

RMTH0 - RMTH2

RST

RTST

SD

SMODE

SRED

TCK

TDI

TDON

TMODE

TMS

TRCK

TRST

TTCK

OUTPUT

DOBUP

FERR

RDT

TDO

INPUT/OUTPUT

DDT0 - DDT15

TBP

TDT0 - TDT9

VBUP

VDT0 - VDT7

: ACTIVITY THRESHOLD

: PB BUP

: BUP

: DIGEST MODE

: TEST DATA SELECT

: DCT RETURN

: EXTERNAL ACTIVITY

: EXTERNAL ACTIVITY ENABLE

: EXTERNAL Q-NUMBER

: EXTERNAL Q-NUMBER ENABLE

: 3-PASS CUT MODE

: RED DETECT (HD)

: IMPACT

: PHASE-1 COMPATIBLE MODE

: PB MOTION THRESHOLD

: POWER SAVE

: REC/PB SELECT (H : REC, L : PB)

: ROUND MODE

: REC MOTION THRESHOLD

: SYSTEM RESET

: RAM TEST

: MODE SETTING

: FOR TEST

: RED DETECT (SD)

: JTAG CLOCK

: JTAG DATA

: TEST DATA OUTPUT ON

: FOR TEST

: JTAG MODE SET

: CLOCK (18 MHz)

: JTAG RESET

: CLOCK (HD : 24 MHz, SD : 18 MHz)

: BUP

: FRAMING ERROR

: RED DETECT FLAG

: JTAG DATA

: DATA (D1/SFY SIDE)

: TEST DATA BUP

: TEST DATA

: BUP (V1 SIDE)

: DATA (V1 SIDE)

CXD8608R (SONY)

Summary of Contents for HSRA-11

Page 6: ......

Page 74: ......

Page 84: ...9 10 9 10 HSR 1 1P HSR 2 2P ...

Page 91: ......

Page 98: ......

Page 109: ......

Page 111: ...10 15 10 15 HSR 1 1P HSR 2 2P CM 56 CM 56 CM 56 B SIDE SUFFIX 11 ...

Page 112: ...10 16 10 16 HSR 1 1P HSR 2 2P ...

Page 115: ...10 19 10 19 HSR 1 1P HSR 2 2P JC 19 C JC 19 C JC 19 C B SIDE SUFFIX 21 ...

Page 116: ...10 20 10 20 HSR 1 1P HSR 2 2P RP 228 RP 228 RP 228 A SIDE SUFFIX 11 ...

Page 118: ......

Page 141: ...2 3 4 5 I J K L M N O P 11 13 b1 11 13 b1 HSR 1 1P HSR 2 2P 1 ...

Page 166: ...2 3 4 5 A B C D E F G H 11 32 b 11 32 b HSR 1 1P HSR 2 2P 1 ...

Page 180: ...2 3 4 5 A B C D E F G H 11 32 a 11 32 a HSR 1 1P HSR 2 2P 1 ...

Page 188: ...2 3 4 5 A B C D E F G H 11 40 11 40 HSR 1 1P HSR 2 2P 1 ...

Page 204: ...11 56 11 56 HSR 1 1P HSR 2 2P JC 19 C 8 9 JC 19 C 8 9 ...

Page 221: ...2 3 4 5 I J K L M N O P 11 73 b 11 73 b HSR 1 1P HSR 2 2P 1 ...

Page 226: ......