7-17

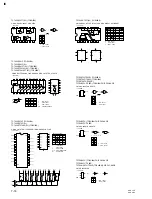

HSR-1/1P

HSR-2/2P

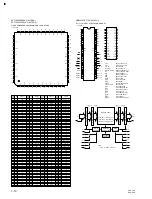

IC

EN

0

1

1

1

1

1

1

1

1

Y7

1

1

1

1

1

1

1

1

0

Y6

1

1

1

1

1

1

1

0

1

Y5

1

1

1

1

1

1

0

1

1

Y4

1

1

1

1

1

0

1

1

1

Y3

1

1

1

1

0

1

1

1

1

Y2

1

1

1

0

1

1

1

1

1

Y1

1

1

0

1

1

1

1

1

1

Y0

1

0

1

1

1

1

1

1

1

C

x

0

0

0

0

1

1

1

1

B

x

0

0

1

1

0

0

1

1

A

x

0

1

0

1

0

1

0

1

V

DD

IN

IN

IN

IN

IN

IN

OUT

INPUTS

OUTPUTS

1

2

3

4

5

6

7

A

B

C

EN1

EN2

EN3

Y7

8

10

11

12

13

14

15

16

9

0

1

x

EN =

EN1

•

EN2

• EN3

GND

OUT

4

1

2

3

15

14

13

A

B

C

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

EN

5

6

EN1

EN2

EN3

Y0

OUT

Y1

OUT

Y2

OUT

Y3

OUT

Y4

OUT

Y5

OUT

Y6

12

11

10

9

7

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

C-MOS 3-TO-8 LINE DECODER/DEMULTIPLEXER

—TOP VIEW—

A

B

A

B

Y =

Y

14

13

V

DD

GND

12

11

10

9

8

7

6

5

4

3

2

1

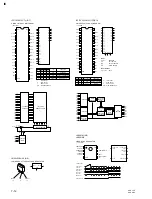

A

0

0

1

1

B

0

1

0

1

Y

1

1

1

0

0 ; LOW LEVEL

1 ; HIGH LEVEL

Y = A • B = A

+

B

C-MOS QUAD 2-INPUT NAND GATES

—TOP VIEW—

G

A

Y

0

0

HI-Z

1

0

1

x

HI-Z

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

: HIGH IMPEDANCE

V

DD

GND

10

9

8

7

6

5

1

2

3

4

11

12

14

13

x

1

1

0

0

Y

A

G

C-MOS BUS BUFFER GATES WITH 3-STATE OUTPUT

—TOP VIEW—

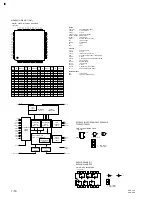

1

16

2EN

IN

15

2

2B

IN

14

3

2Y0

OUT

13

4

12

5

11

6

10

7

9

8

1EN

IN

V

DD

4

5

2

3

A

B

Y0

Y1

GND

1A

IN

1B

IN

1Y0

OUT

1Y1

OUT

1Y2

OUT

1Y3

OUT

2A

IN

2Y1

OUT

2Y2

OUT

2Y3

OUT

Y2

6

Y3

7

9

Y3

10

Y2

Y1

Y0

B

A

13

14

11

12

EN

1

15

EN

INPUTS

B

A

EN

OUTPUTS

Y2

Y0

Y1

Y3

1

1

0

1

0

0

0

0

0

0

0

1

1

1

1

1

1

1

0

1

x

x

1

1

1

1

1

1

1

1

1

0

0

0

1

C-MOS DUAL 2-TO-4 DECODER/DEMULTIPLEXER

—TOP VIEW—

0

1

x

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

1

2

3

4

5

6

7

8

INH

X

IN

B

IN

X3

IN

X2

IN

X1

IN

X0

IN

XC

OUT

GND

16

15

14

13

12

11

10

9

INH

Y

IN

A

IN

Y3

IN

Y2

IN

Y1

IN

Y0

IN

YC

OUT

V

DD

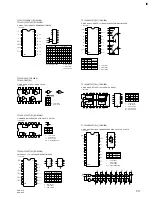

CONTROL IN

INH

0

0

0

0

1

B

0

0

1

1

x

A

0

1

0

1

x

ON

CHANNEL

0

1

2

3

GND

0

1

x

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

1

6

5

4

3

14

2

10

11

12

13

15

INH

X

X0

X1

X2

X3

A

B

Y0

Y1

Y2

Y3

INH

Y

7

XC

9

YC

C-MOS DUAL 4-LINE-TO-1-LINE DATA SELECTOR/MULTIPLEXER

—TOP VIEW—

16

V

DD

Q4

Q4

D4

D3

Q3

Q3

CK

GND

9

10

15

14

13

12

11

1

8

7

2

3

4

5

6

RD

RD

Q

Q

RD

D

Q

RD

Q

D

Q

Q

Q

D

D

RD

Q1

Q1

D1

D2

Q2

Q2

0

1

x

Q

0

Q

0

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

: NO CHANGE

: NO CHANGE

4

5

12

13

11

15

9

2

3

7

6

10

D1

D2

D4

D3

Q1

Q1

Q3

Q4

14

Q4

Q3

Q2

Q2

1

RD

Q

C-MOS QUAD D-TYPE FLIP-FLOPS WITH RESET

—TOP VIEW—

RD

0

1

1

1

CK

x

0

D

x

1

0

x

Q

0

1

0

Q

0

Q

1

0

1

Q

0

TC74HC138AF(EL) (TOSHIBA)

TC74VHC138FT(EL) (TOSHIBA)

TC74VHC00F (TOSHIBA)

TC74VHC00F(EL)

TC74VHC125FT(EL) (TOSHIBA)

TC74VHC139FT(EL) (TOSHIBA)

TC74VHC153FT(EL) (TOSHIBA)

TC74VHC175FT(EL) (TOSHIBA)

B1

18

A1

2

1

2

3

4

5

6

7

8

9

10

17

A2

3

B3

16

A3

4

B4

15

A4

5

B5

14

A5

6

B6

13

A6

7

B7

12

A7

8

B8

11

A8

9

19

1

EN

DIR

20

19

18

17

16

15

14

13

12

11

DIR

IN

A1

A2

A3

A4

A5

A6

A7

A8

EN

IN

B1

B2

B3

B4

B5

B6

B7

B8

GND

V

DD

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

DIR

DIR

A

B

DIR

EN

1

19

EN

0

0

1

DIR

0

1

x

OPERATION

B to A

A to B

HI-Z

0

1

x

HI-Z

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

: HIGH IMPEDANCE

B2

C-MOS BILATERAL BUS TRANSCEIVERS WITH 3-STATE OUTPUTS

—TOP VIEW—

TC74VHC245FT(EL) (TOSHIBA)

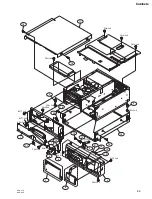

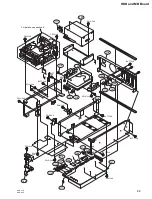

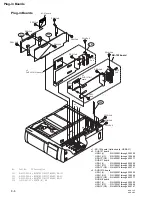

Summary of Contents for HSRA-11

Page 6: ......

Page 74: ......

Page 84: ...9 10 9 10 HSR 1 1P HSR 2 2P ...

Page 91: ......

Page 98: ......

Page 109: ......

Page 111: ...10 15 10 15 HSR 1 1P HSR 2 2P CM 56 CM 56 CM 56 B SIDE SUFFIX 11 ...

Page 112: ...10 16 10 16 HSR 1 1P HSR 2 2P ...

Page 115: ...10 19 10 19 HSR 1 1P HSR 2 2P JC 19 C JC 19 C JC 19 C B SIDE SUFFIX 21 ...

Page 116: ...10 20 10 20 HSR 1 1P HSR 2 2P RP 228 RP 228 RP 228 A SIDE SUFFIX 11 ...

Page 118: ......

Page 141: ...2 3 4 5 I J K L M N O P 11 13 b1 11 13 b1 HSR 1 1P HSR 2 2P 1 ...

Page 166: ...2 3 4 5 A B C D E F G H 11 32 b 11 32 b HSR 1 1P HSR 2 2P 1 ...

Page 180: ...2 3 4 5 A B C D E F G H 11 32 a 11 32 a HSR 1 1P HSR 2 2P 1 ...

Page 188: ...2 3 4 5 A B C D E F G H 11 40 11 40 HSR 1 1P HSR 2 2P 1 ...

Page 204: ...11 56 11 56 HSR 1 1P HSR 2 2P JC 19 C 8 9 JC 19 C 8 9 ...

Page 221: ...2 3 4 5 I J K L M N O P 11 73 b 11 73 b HSR 1 1P HSR 2 2P 1 ...

Page 226: ......