83

DVP-CX995V

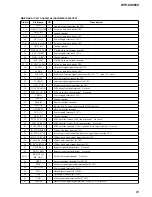

MB BOARD IC304 uPD703260-YGF-S30-JBT-A (SYSTEM CONTROLLER)

Pin No.

Pin Name

I/O

Description

1, 2

KEY1, KEY0

I

Front panel keys input terminal (A/D input)

3

AVDD

-

Power supply terminal (+3.3V)

4

AVSS

-

Ground terminal

5, 6

NC

O

Not used

7

AVREF

I

Reference voltage (+3.3V) input terminal

8

JOG_A

I

Jog dial pulse input from the rotary encoder (A phase input)

9

JOG_B

I

Jog dial pulse input from the rotary encoder (B phase input)

10

FLMD0

I

Flash memory data write mode control signal input terminal

11

VDD

-

Power supply terminal (+3.3V)

12

REGC

O

Connection terminal to the regulator capacitor

13

VSS

-

Ground terminal

14

5.0M

I

System clock input terminal (5 MHz)

15

5.0M

O

System clock output terminal (5 MHz)

16

RESET

I

System reset signal input from the reset signal generator "L": reset

For several hundreds msec. after the power supply rises, "L" is input, then it change to "H"

17

GND

-

Ground terminal

18

OPEN

-

Not used

19

HDMI_RST

O

Reset signal output terminal Not used

20

KEY_INT

I

Wake up signal input from front panel keys or remote commander

21

232C_INT

I

Wake up signal input terminal for RS-232C Not used

22

DEBUGRST

O

Reset signal output terminal Not used

23

BE_CS

O

Chip select signal output to the CPU

24

SIN

I

Serial data input terminal when data writing to internal ROM Not used

25

SOUT

O

Serial data output terminal when data writing to internal ROM Not used

26

SCLK

I

Serial data transfer clock signal input terminal when data writing to internal ROM Not used

27

232COUT

O

Transmit data output terminal for RS-232C Not used

28

232CIN

I

Receive data input terminal for RS-232C Not used

29

DSENS_OUT

O

Disc sensor signal output terminal for the adjustment

30

HH_OUT

O

Signal output terminal for the adjustment

31

SIRCS

I

Remote control signal input from the remote control receiver

32

NC

O

Not used

33

BE_BUSY

I

Busy signal input from the CPU

34

BE_RST

O

Reset signal output to the flash memories, CPU and D/A converter "L": reset

35

EVSS

-

Ground terminal

36

EVDD

-

Power supply terminal (+3.3V)

37

DDC_SDA

I/O

I2C data bus terminal Not used

38

DDC_SCL

O

I2C bus clock signal output terminal Not used

39

TBM+

O

Table motor drive signal output terminal "H": motor on

40

TBM-

O

Table motor drive signal output terminal "H": motor on

41 to 44

NC

O

Not used

45

BE_TXD

O

UART transmit data output to the CPU

46

BE_RXD

I

UART receive data input from the CPU

47

DRM+

O

Door motor drive signal output terminal "H": motor on

48

DRM-

O

Door motor drive signal output terminal "H": motor on

49

LDM+

O

Loading motor drive signal output terminal "H": motor on

50

LDM-

O

Loading motor drive signal output terminal "H": motor on