SN8P2318 Series

C-type LCD, RFC 8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD

Page 83

Version 1.5

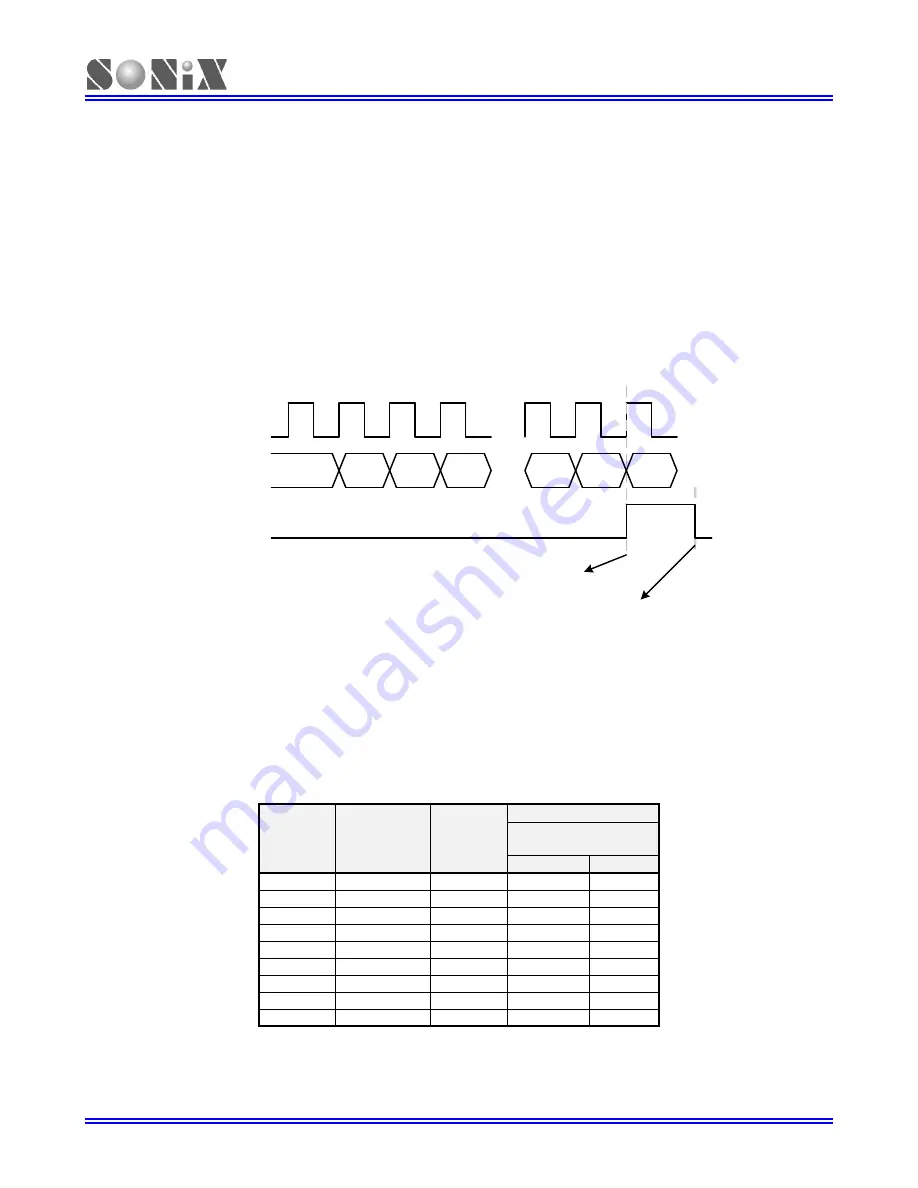

8.3.2 TC0 TIMER OPERATION

TC0 timer is controlled by TC0ENB bit. When TC0ENB=0, TC0 timer stops. When TC0ENB=1, TC0 timer starts to

count. Before enabling TC0 timer, setup TC0 timer

’s configurations to select timer function modes, e.g. basic timer,

interrupt function

…TC0C increases “1” by timer clock source. When TC0 overflow event occurs, TC0IRQ flag is set

as

”1” to indicate overflow and cleared by program. The overflow condition is TC0C count from full scale (0xFF) to zero

scale (0x00). In difference function modes, TC0C value relates to operation. If TC0C value changing effects operation,

the transition of operations would make timer function error. So TC0 builds in double buffer to avoid these situations

happen. The double buffer concept is to flash TC0C during TC0 counting, to set the new value to TC0R (reload buffer),

and the new value will be loaded from TC0R to TC0C after TC0 overflow occurrence automatically. In the next cycle,

the TC0 timer runs under new conditions, and no any transitions occur. The auto-reload function is no any control

interface and always actives as TC0 enables. If TC0 timer interrupt function is enabled (TC0IEN=1), the system will

execute interrupt procedure. The interrupt procedure is system program counter points to interrupt vector (ORG 8) and

executes interrupt service routine after TC0 overflow occurrence. Clear TC0IRQ by program is necessary in interrupt

procedure. TC0 timer can works in normal mode, slow mode and green mode. But in green mode, TC0 keep counting,

set TC0IRQ and outputs PWM, but can

’t wake-up system.

0x00

or TC0R

...

...

Clock

Source

TC0C

TC0IRQ

TC0 timer overflows. TC0IRQ set as “1”.

Reload TC0C from TC0R automatically.

TC0IRQ is cleared by program.

0x01

0x02

0x03

0xFE

0xFF

TC0R

...

...

TC0 provides different clock sources to implement different applications and configurations. TC0 clock source includes

Fcpu (instruction cycle), Fhosc (high speed oscillator) and external input pin (P0.0) controlled by TC0CKS[1:0] bits.

TC0CKS0 bit selects the clock source is from Fcpu or Fhosc. If TC0CKS0=0, TC0 clock source is Fcpu through

TC0rate[2:0] pre-scaler to decide Fcpu/1~Fcpu/128. If TC0CKS0=1, TC0 clock source is Fhosc without any divider.

TC0CKS1 bit controls the clock source is external input pin or controlled by TC0CKS0 bit. If TC0CKS1=0, TC0 clock

source is selected by TC0CKS0 bit. If TC0CKS1=1, TC0 clock source is external input pin that means to enable event

counter function. TC0rate[2:0] pre-scaler is unless when TC0CKS0=1 or TC0CKS1=1 conditions. TC0 length is 8-bit

(256 steps), and the one count period is each cycle of input clock.

TC0CKS0 TC0rate[2:0] TC0 Clock

TC0 Interval Time

Fhosc=16MHz,

Fcpu=Fhosc/2

max. (ms) Unit (us)

0

000b

Fcpu/128

4.096

16

0

001b

Fcpu/64

2.048

8

0

010b

Fcpu/32

1.024

4

0

011b

Fcpu/16

0.512

2

0

100b

Fcpu/8

0.256

1

0

101b

Fcpu/4

0.128

0.5

0

110b

Fcpu/2

0.064

0.25

0

111b

Fcpu/1

0.032

0.125

1

useless

Fhosc

0.016

0.0625