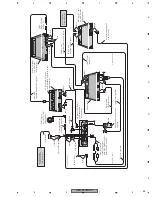

DEQ-P8000/UC

37

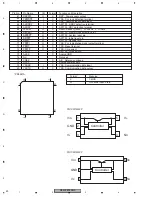

5

6

7

8

5

6

7

8

C

D

F

A

B

E

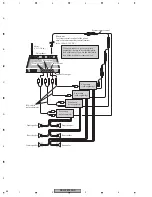

D I R M C K

DDIN0

DDIN1

DDIN2

DDIN3

V

ERR/BS

DBL/V

DIRINT

D I R B C K

D I R W C K

S D W C K I 0

S D B C K I 0

/ S D B C K O

D I R P C O

D I R S D O

S D I A

S U R E N C

K A R A O K E

M U T E

C R C

A C 3 D A T A

D T S D A T A

N O N P C M

Z E R O F L G

X I

X O

C P O

S D O A 0

S D O A 1

S D O A 2

S D I B 0

S D I B 1

S D I B 2

S D I B 3

R A M D 0 - 1 5

C A S N

R A S N

R A M W E N

R A M O E N

R A M A 0 - 1 7

O V F B / E N D

SDOB3

SDOB2

SDOB1

SDOB0

SDWCKI1

SDBCKI1

O P O R T 0 - 7

/ C S

S O

S I

S C K

I P O R T 0 - 4

D B L

ERR

BS

SYNC

U

FS128

C

SYNC/U

FS128/C

VMOD

BSMOD

DDINSEL

UMOD

IPORT5-7

7

6

5

CMOD

CRC

PLL

PLL

DIR

SDIASEL

MainDSP

(AC-3/ProLogicII/

DTS Decoder)

Coefficient.

Program

RAM

SDIBSEL

SubDSP

SDIBCKSEL

SDOBCKSEL

OVFSEL

Control Resistor

MPLOAD

Microcomputer Interface

Memory

Interface

SDIACKSEL

DIRO Interface

SDIA Interface

SDOA Interface

SDIB Interface

SDOB Interface

DIR Clock

(25MHz)

DSP Clock

(30MHz)

L,R

LS,RS

C,LFE

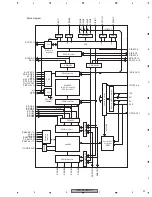

Block diagram

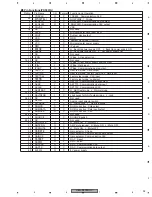

Summary of Contents for DEQ-P6600/EW

Page 4: ...DEQ P8000 UC 4 1 2 3 4 1 2 3 4 C D F A B E 1 SPECIFICATIONS ...

Page 5: ...DEQ P8000 UC 5 5 6 7 8 5 6 7 8 C D F A B E ...

Page 6: ...DEQ P8000 UC 6 1 2 3 4 1 2 3 4 C D F A B E ...

Page 7: ...DEQ P8000 UC 7 5 6 7 8 5 6 7 8 C D F A B E ...

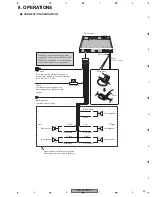

Page 10: ...DEQ P8000 UC 10 1 2 3 4 1 2 3 4 C D F A B E 2 2 EXTERIOR ...

Page 22: ...DEQ P8000 UC 22 1 2 3 4 1 2 3 4 C D F A B E A A AUDIO CONTROL UNIT IC Q ...

Page 23: ...DEQ P8000 UC 23 5 6 7 8 5 6 7 8 C D F A B E A SIDE B ...