2004 Mar 01

61

Philips Semiconductors

Product specification

Digital video encoder

SAA7102; SAA7103

8

BOUNDARY SCAN TEST

The SAA7102; SAA7103 has built-in logic and 5 dedicated

pins to support boundary scan testing which allows board

testing without special hardware (nails). The SAA7102;

SAA7103 follows the

“IEEE Std. 1149.1 - Standard Test

Access Port and Boundary-Scan Architecture” set by the

Joint Test Action Group (JTAG) chaired by Philips.

The 5 special pins are Test Mode Select (TMS), Test

Clock (TCK), Test Reset (TRST), Test Data Input (TDI)

and Test Data Output (TDO).

The Boundary Scan Test (BST) functions BYPASS,

EXTEST, INTEST, SAMPLE, CLAMP and IDCODE are all

supported; see Table 112. Details about the

JTAG BST-TEST can be found in the specification “

IEEE

Std. 1149.1”. A file containing the detailed Boundary Scan

Description Language (BSDL) of the SAA7102; SAA7103

is available on request.

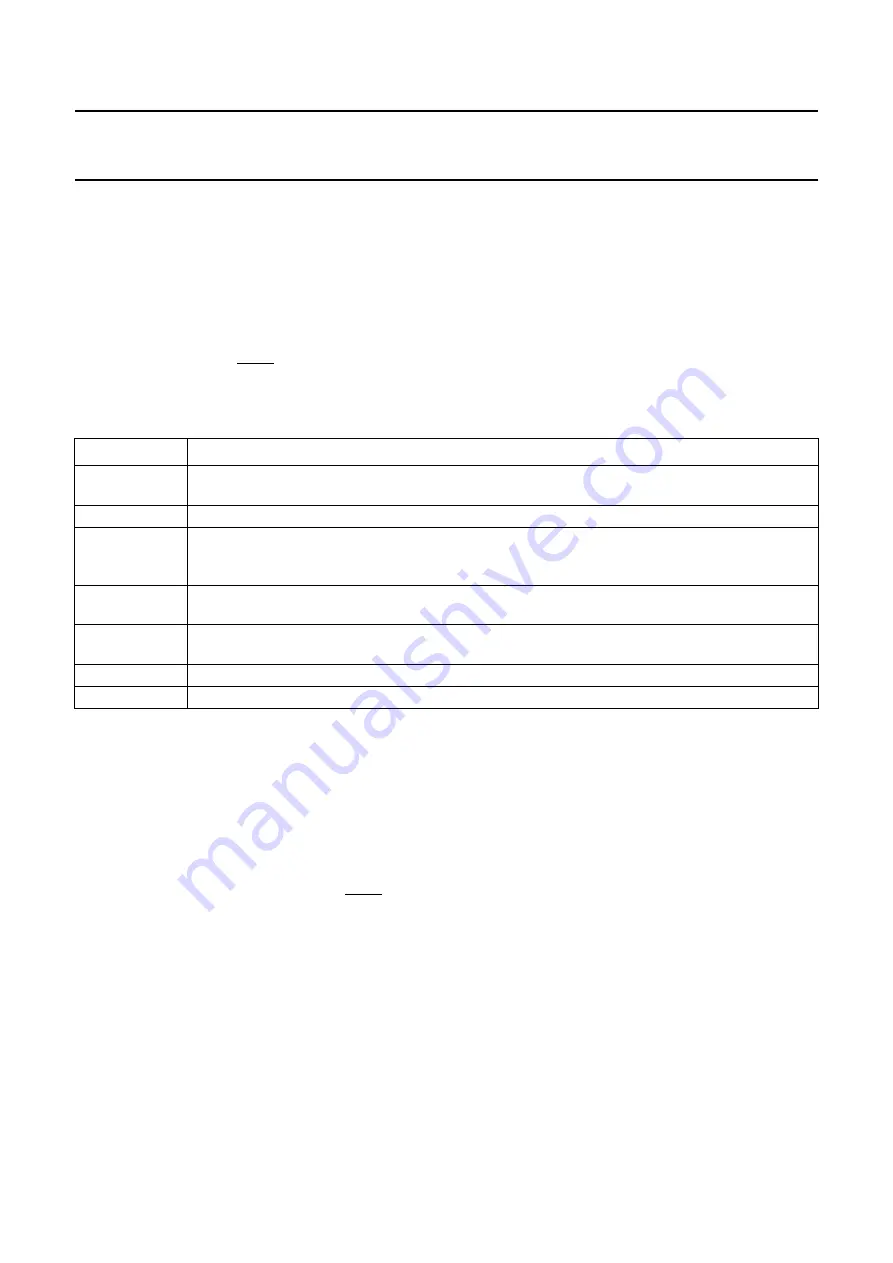

Table 112 BST instructions supported by the SAA7102; SAA7103

INSTRUCTION

DESCRIPTION

BYPASS

This mandatory instruction provides a minimum length serial path (1 bit) between TDI and TDO

when no test operation of the component is required.

EXTEST

This mandatory instruction allows testing of off-chip circuitry and board level interconnections.

SAMPLE

This mandatory instruction can be used to take a sample of the inputs during normal operation of

the component. It can also be used to preload data values into the latched outputs of the

boundary scan register.

CLAMP

This optional instruction is useful for testing when not all ICs have BST. This instruction addresses

the bypass register while the boundary scan register is in external test mode.

IDCODE

This optional instruction will provide information on the components manufacturer, part number and

version number.

INTEST

This optional instruction allows testing of the internal logic (no support for customer available).

USER1

This private instruction allows testing by the manufacturer (no support for customer available).

8.1

Initialization of boundary scan circuit

The Test Access Port (TAP) controller of an IC should be

in the reset state (TEST_LOGIC_RESET) when the IC is

in functional mode. This reset state also forces the

instruction register into a functional instruction such as

IDCODE or BYPASS.

To solve the power-up reset, the standard specifies that

the TAP controller will be forced asynchronously to the

TEST_LOGIC_RESET state by setting the TRST pin

LOW.

8.2

Device identification codes

A device identification register is specified in

“IEEE Std.

1149.1b-1994”. It is a 32-bit register which contains fields

for the specification of the IC manufacturer, the IC part

number and the IC version number. Its biggest advantage

is the possibility to check for the correct ICs mounted after

production and to determine the version number of the ICs

during field service.

When the IDCODE instruction is loaded into the BST

instruction register, the identification register will be

connected between TDI and TDO of the IC. The

identification register will load a component specific code

during the CAPTURE_DATA_REGISTER state of the TAP

controller, this code can subsequently be shifted out. At

board level this code can be used to verify component

manufacturer, type and version number. The device

identification register contains 32 bits, numbered 31 to 0,

where bit 31 is the most significant bit (nearest to TDI) and

bit 0 is the least significant bit (nearest to TDO);

see Fig.10.